# Tempus M24

MEMORY LIGHTING CONTROL

MAINTENANCE HANDBOOK

**TECHNICAL INFORMATION**

# Rank Strand

# Tempus M24

MEMORY LIGHTING CONTROL

MAINTENANCE HANDBOOK

| М | _ | A | 3.4 | a | a  |

|---|---|---|-----|---|----|

| м | 1 | 4 | 10  | и | V. |

# TEMPUS M24 MEMORY LIGHTING CONTROL

# MAINTENANCE HANDBOOK

#### CONTENTS

# CHAPTER 1 - INTRODUCTION

| 1.1     | GENERAL                             | 1 |

|---------|-------------------------------------|---|

| 1.1.1   | Patch/Effects System                | 2 |

| 1.2     | CONSTRUCTION                        | 2 |

| 1.2.1   | Control Console                     | 2 |

| 1.2.2   | Multiplex Interface Unit            | 3 |

| 1.2.2.1 | Connections                         | 4 |

| 1.2.3   | M24Fx Patch/Effects Unit            | 4 |

| 1.2.3.1 | Connections                         | 5 |

| 1.3     | SPECIFICATION                       | 5 |

| 1.4     | USING THE HANDBOOK                  | 8 |

| 1.4.1   | Glossary of Terms                   | 8 |

|         | CHAPTER 2 - SYSTEMS DESCRIPTION     |   |

| 2.1     | INTRODUCTION                        | 1 |

| 2.2     | CONTROL CONSOLE                     | 1 |

| 2.2.1   | Power Supplies                      | 1 |

| 2.2.2   | Panel Board                         | 1 |

| 2.2.2.1 | Address Map                         | 2 |

| 2.2.2.2 | Panel Processor Program             | 4 |

| 2.2.3   | Motherboard and Executive Processor | 7 |

| 2.2.3.1 | Address Map                         | 7 |

| 2.2.3.2 | Panel Communication Interface       | 8 |

| 2.2.3.3 | Mage Interface                      | 9 |

Issue 1

| Page 2  |                                          | M24M00 |

|---------|------------------------------------------|--------|

|         |                                          |        |

| 2.2.3.4 | Analogue Interface                       | 9      |

| 2.2.3.5 | Motherboard Processor Program            | 11     |

| 2.2.4   | Panel/Motherboard Communication          | 13     |

| 2.2.4.1 | Communication Format                     | 14     |

| 2.2.4.2 | Control Bytes                            | 14     |

| 2.2.4.3 | Sync Byte                                | 15     |

| 2.2.5   | Video Interface                          | 15     |

| 2.3     | MULTIPLEX INTERFACE UNIT                 | 18     |

| 2.3.1   | Channel Demultiplexer                    | 18     |

| 2.3.2   | Channel Multiplexer                      | 19     |

| 2.3.3   | Independent Operation                    | 19     |

| 2.4     | M24Fx PATCH/EFFECTS UNIT                 | 19     |

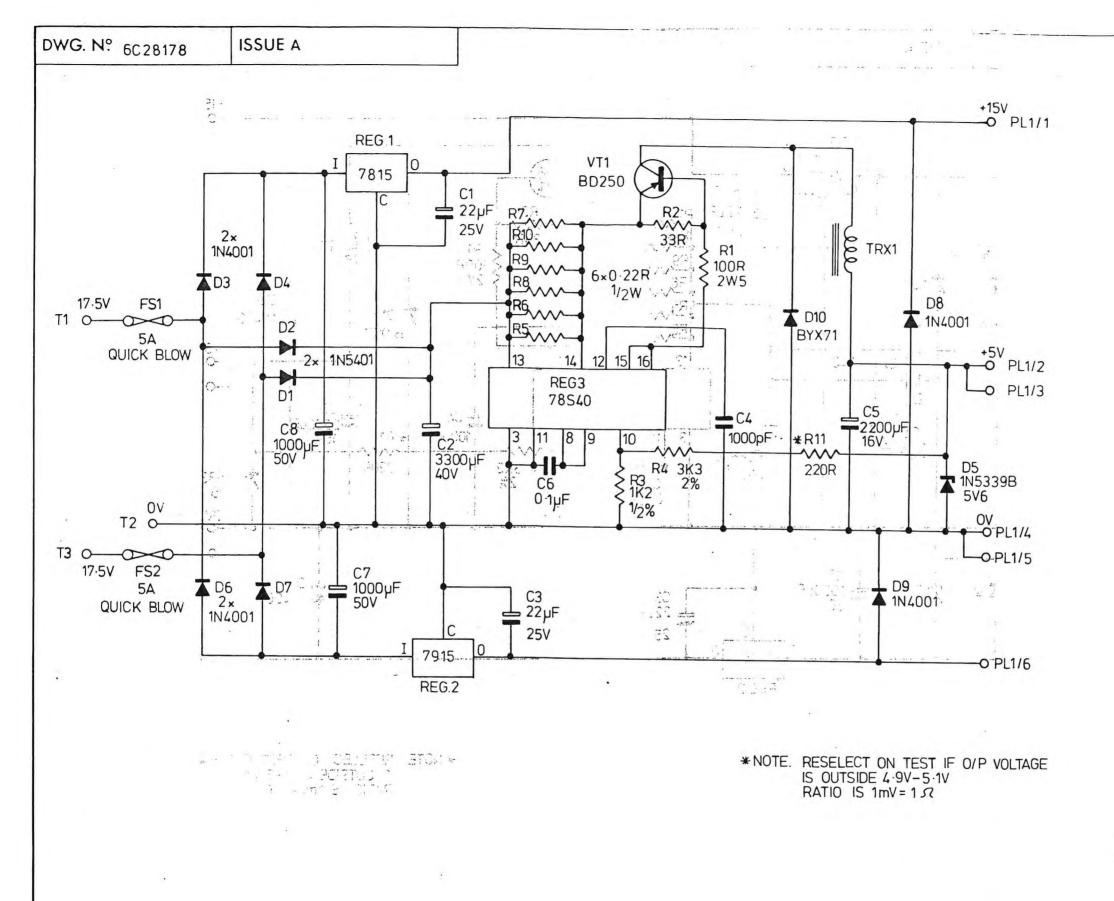

| 2.4.1   | Power Supplies                           | 19     |

| 2.4.2   | Effects Processor Board                  | 20     |

| 2.4.2.1 | Address Map                              | 20     |

| 2.4.2.2 | Patch Master Faders                      | 22     |

| 2.4.2.3 | Effects System                           | 22     |

| 2.4.2.4 | Sync Detector                            | 24     |

| 2.4.2.5 | Effects Processor Program                | 24     |

|         | CHAPTER 3 - CONTROL PANEL BOARD          |        |

| 3.1     | INTRODUCTION                             | 1      |

| 3.2     | THE MICROPROCESSOR                       | 1      |

| 3.3     | PANEL PROCESSOR ADDRESSES                | 2      |

| 3.3.1   | Program PROM                             | 2      |

| 3.3.2   | External RAM                             | 3      |

| 3.3.3   | Wheel Interface                          | 3      |

| 3.3.4   | Interrupt Latch                          | 3      |

| 3.3.5   | Address Locations within the MPU         | 3      |

| 3.4     | SERIAL COMMUNICATIONS INTERFACE          | 4      |

| 3.5     | DISPLAY AND PUSH-BUTTON MATRICES         | 4      |

| 3.5.1   | Display Matrix                           | 5      |

| 3.5.2   | Button Matrix                            | 5      |

| 3.5.3   | Display and Contact Scan                 | - 6    |

| 3.6     | MASTER FADERS AND FADE DURATION CONTROLS | 7      |

| 3.7     | RESET CIRCUIT                            | 7      |

|         |                                          |        |

# CHAPTER 4 - WHEEL INTERFACE BOARD

| 4.1     | INTRODUCTION                    | 1  |

|---------|---------------------------------|----|

| 4.2     | MOVEMENT DETECTOR               | 1  |

| 4.3     | THE COUNT PROCESS               | 3  |

| 1.4     | COUNT LIMIT DETECTION           | 3  |

| 4.5     | MICROPROCESSOR READ ACTION      | 4  |

|         | CHAPTER 5 - MOTHERBOARD         |    |

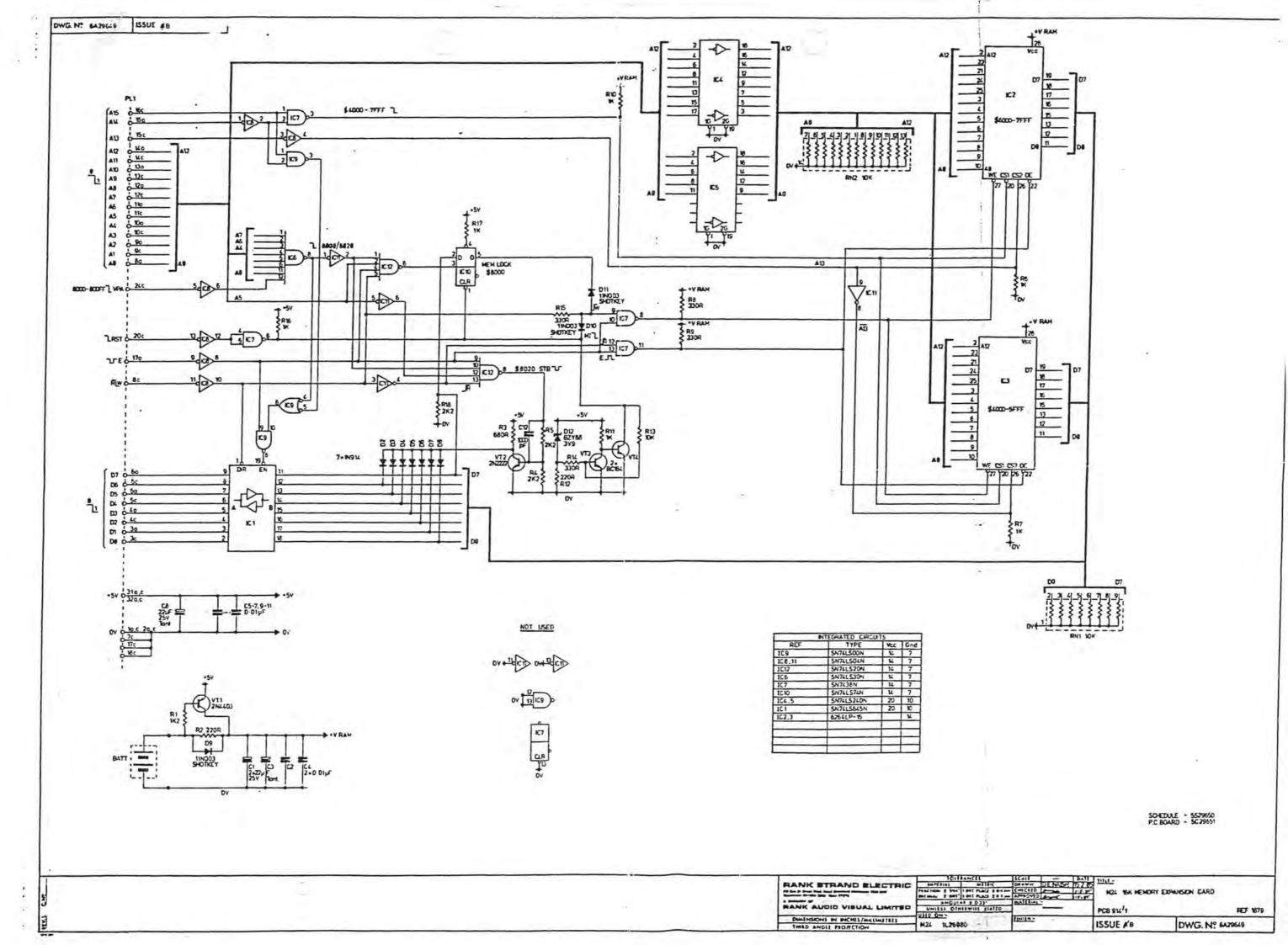

| 5.1     | INTRODUCTION                    | 1  |

| 5.2     | THE MICROPROCESSOR              | 1  |

| 5.3     | MOTHERBOARD PROCESSOR ADDRESSES | 2  |

| 5.3.1   | Kernel PROM Addresses           | 2  |

| 5.3.2   | Paged PROM Addresses (Page 0)   | 3  |

| 5.3.3   | RAM Addresses                   | 3  |

| 5.3.3.1 | Memory Lock                     | 4  |

| 5.3.3.2 | Reset Write Inhibit             | 5  |

| 5.3.3.3 | RAM Bus Buffers                 | 5  |

| 5.3.3.4 | Battery Circuit                 | 6  |

| 5.3.4   | Peripheral Interface Addresses  | 6  |

| 5.4     | SYSTEM BUS INTERFACE            | 7  |

| 5.5     | PERIPHERAL INTERFACE ADAPTER    | 9  |

| 5.6     | PANEL COMMUNICATION INTERFACE   | 10 |

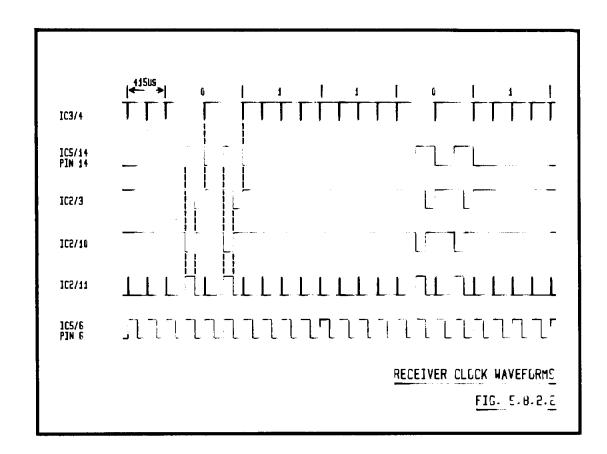

| 5.6.1   | Transmit/Receive Clock          | 10 |

| 5.7     | ANALOGUE INTERFACE              | 11 |

| 5.7.1   | Multiplexed Analogue Output     | 11 |

| 5.7.1.1 | Reference Voltage               | 11 |

| 5.7.1.2 | Sync Pulses                     | 11 |

| 5.7.2   | Analogue Input                  | 12 |

| 5.7.2.1 | Fader Full Reference Voltage    | 14 |

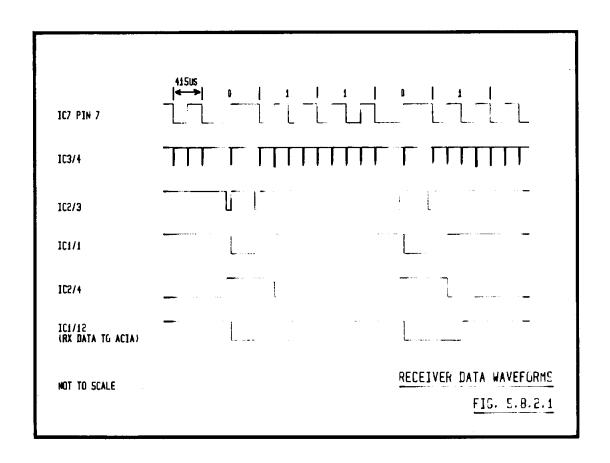

| 5.8     | TAPE INTERFACE                  | 14 |

| 5.8.1   | Transmitter Circuit             | 14 |

| 5.8.2   | Receiver Circuit                | 15 |

| 5.8.3   | Audio Test Circuit              | 17 |

| 5.9     | RESET CIRCUIT                   | 18 |

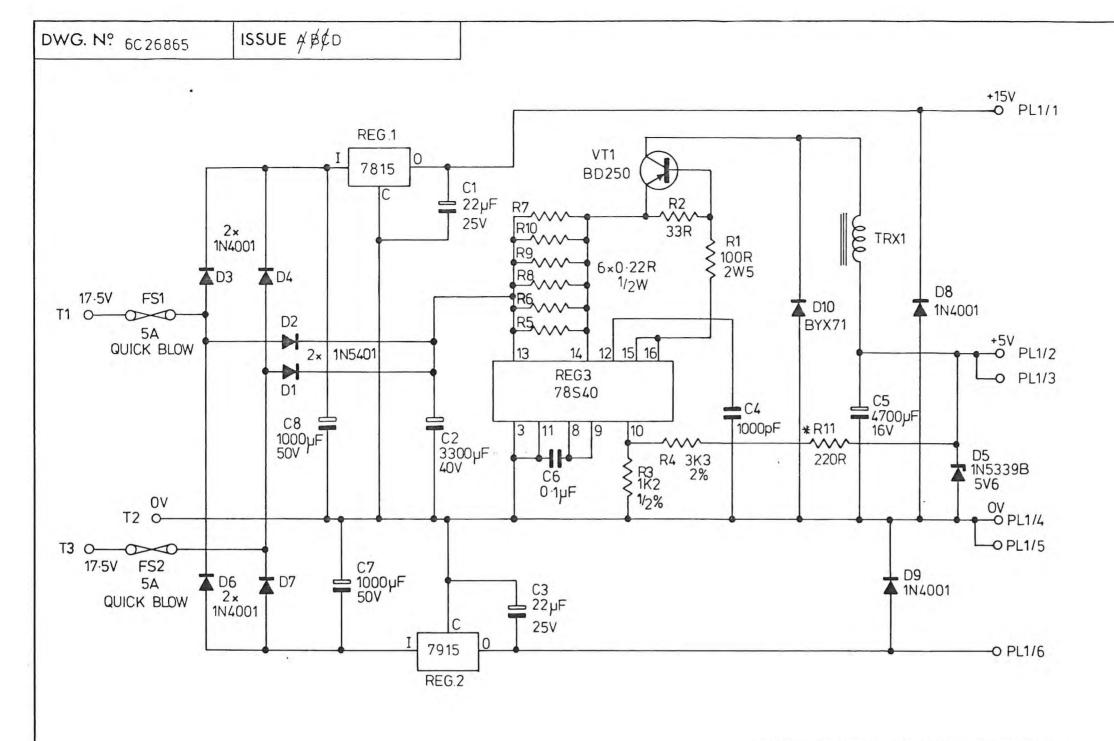

|       | CHAPTER 6 - POWER SUPPLY BOARD          |     |  |

|-------|-----------------------------------------|-----|--|

| 6.1   | INTRODUCTION                            | 1   |  |

| 6.2   | +15V AND -15V SUPPLIES                  | 1   |  |

| 6.3   | +5V SUPPLY                              | 1   |  |

|       | CHAPTER 7 - VIDEO INTERFACE             |     |  |

| 7.1   | INTRODUCTION                            | 1   |  |

| 7.1.1 | Principle of Operation                  | 1   |  |

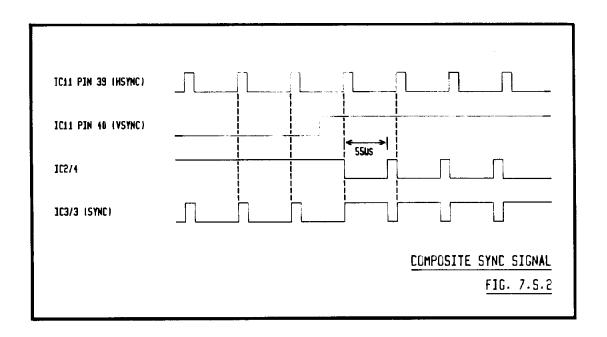

| 7.1.2 | Video Signal                            | 2   |  |

| 7.2   | VIDEO INTERFACE ADDRESSES               | 2 . |  |

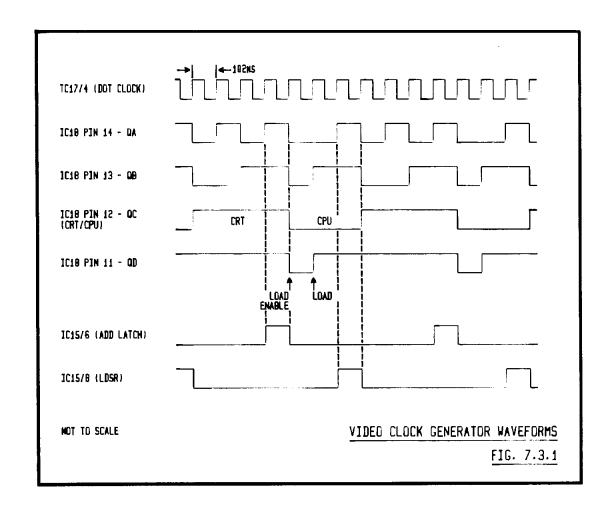

| 7.3   | VIDEO CLOCK GENERATOR                   | 2   |  |

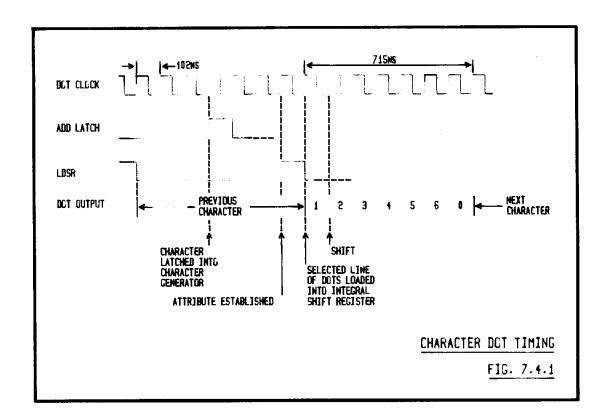

| 7.4   | VIDEO SCAN                              | 3   |  |

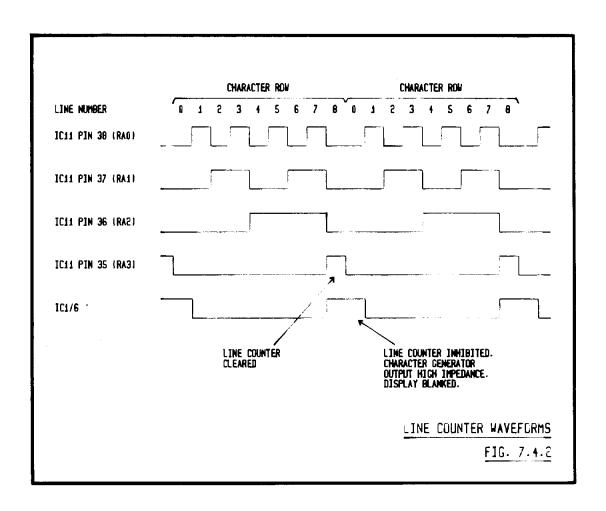

| 7.4.1 | Character Line Synchronisation          | 4   |  |

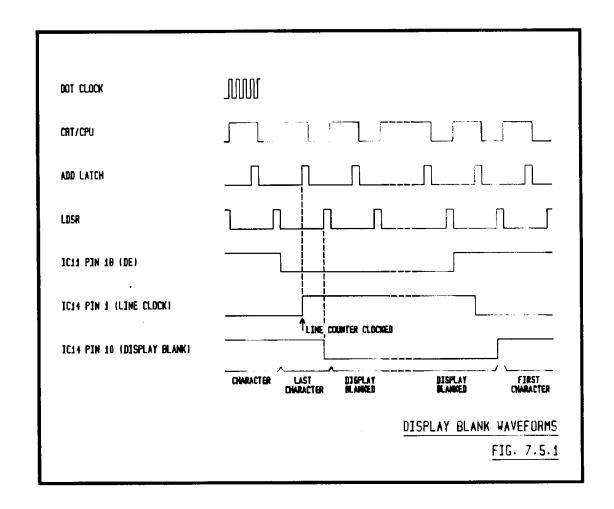

| 7.5   | VIDEO OUTPUT                            | 6   |  |

| 7.5.1 | Character Attributes                    | 7   |  |

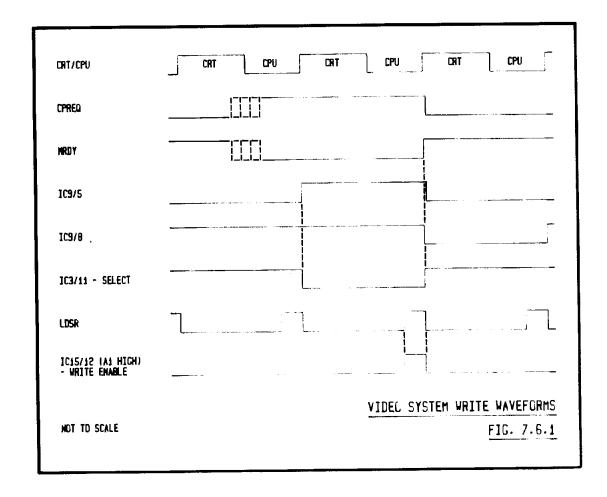

| 7.6   | MPU ACCESS TO THE VIDEO SYSTEM          | 8   |  |

| 7.6.1 | Loading Display Characters into the RAM | 10  |  |

| 7.6.2 | CRTC Initialisation                     | 11  |  |

| 7.7   | VIDEC MODULATOR BOARD                   | 11  |  |

|       | CHAPTER 8 - MULTIPLEX/DEMULTIPLEX BOARD |     |  |

| 8.1   | INTRODUCTION                            | ·1  |  |

| 8.2   | MULTIPLEXED ANALOGUE INPUT              | 1   |  |

| 8.2.1 | Channel Sync Pulses                     | 1.  |  |

| 8.2.2 | Analogue Sampling                       | 2   |  |

| 8.2.3 | Output Enable                           | 3   |  |

| 8.2.4 | Dimmer Drive Outputs                    | 6   |  |

| 8.2.5 | Frame Sync                              | 6   |  |

| 8.3   | MULTIPLEXED ANALOGUE OUTPUT             | 7   |  |

| 8.3.1 | Analogue Inputs                         | 7   |  |

| 8.3.2 | Multiplexed Output                      | 7   |  |

| 8.3.3 | Output Disable                          | 8   |  |

| 8.3.4 | MUX OK Indicator                        | 8   |  |

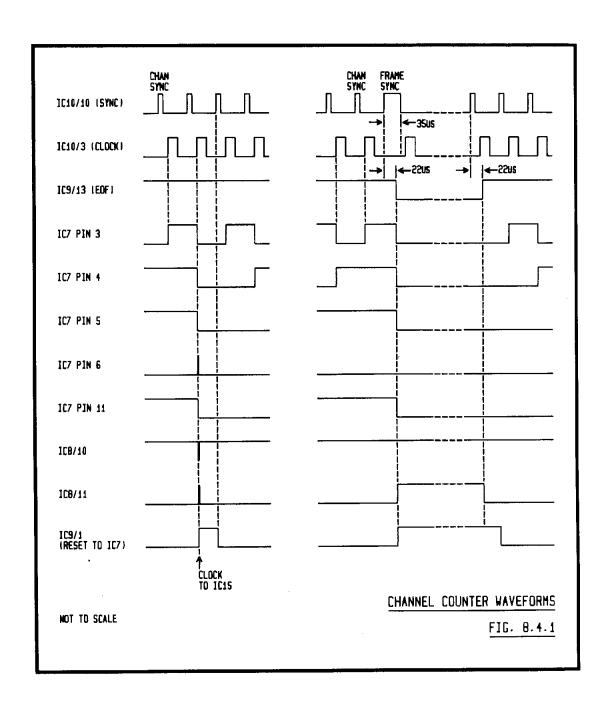

| 8.4   | CHANNEL COUNTER                         | 10  |  |

| 8.4.1 | Card Enable                             | 12  |  |

| 8.5   | INDEPENDENT OPERATION                   | 12  |  |

|       |                                         |     |  |

| M24M00 |                                     | Page 5 |

|--------|-------------------------------------|--------|

|        |                                     |        |

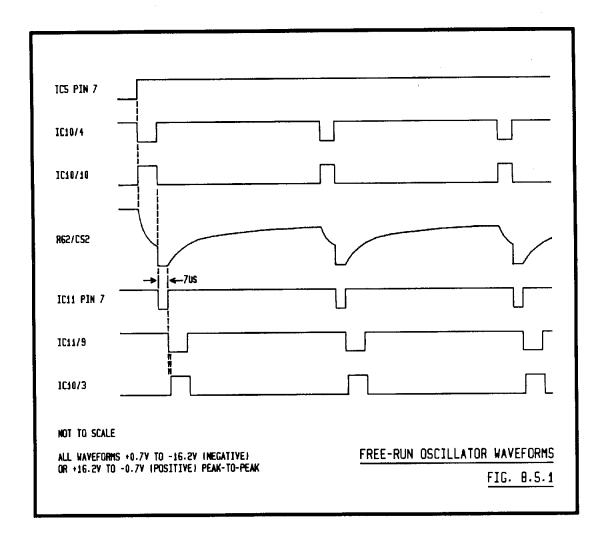

| 8.5.1  | Free-run Oscillator                 | 13     |

| 8.6    | POWER-UP INHIBIT                    | 14     |

| 8.7    | POWER SUPPLIES                      | 15     |

| 8.7.1  | Detailed Circuit Description        | 16     |

|        | CHAPTER 9 - EFFECTS PROCESSOR BOARD |        |

| 9.1    | INTRODUCTION                        | 1      |

| 9.2    | THE MICROPROCESSOR                  | 1      |

| 9.3    | EFFECTS PROCESSOR ADDRESSES         | 1      |

| 9.3.1  | Program PROM                        | 2      |

| 9.3.2  | Alpha-numeric Display               | 3      |

| 9.3.3  | Peripheral Interface Adapters       | 3      |

| 9.3.4  | Random Access Memory                | 3      |

| 9.3.4. | l Battery Circuit                   | 4      |

| 9.4    | PANEL INTERFACE                     | 4      |

| 9.4.1  | Button Matrix                       | 4      |

| 9.4.2  | Indicators                          | 5      |

| 9.5    | PATCH MASTER FADERS                 | 5      |

| 9.5.1  | Master Level Indicators             | 6      |

| 9.6    | EFFECTS SYSTEM                      | 6      |

| 9.6.1  | Effects Master Fader                | 7      |

| 9.6.2  | Chaser                              | 7      |

| 9.6.3  | Flash Generator                     | 8      |

| 9.6.4  | Sound-to-light Generator            | 8      |

| 9.6.4. | l Random Flicker                    | 9      |

| 9.6.5  | Flash Buttons                       | 9      |

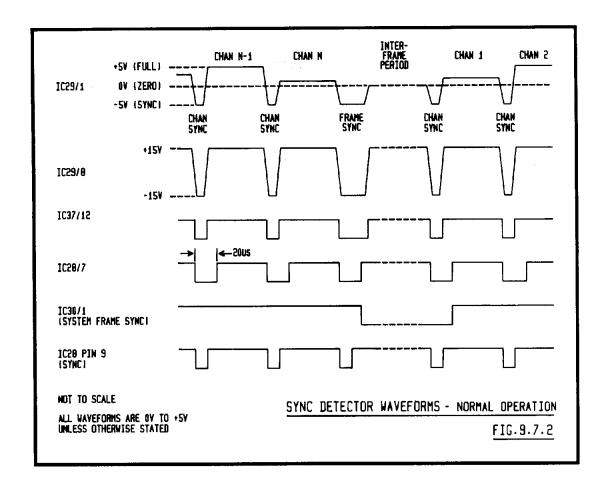

| 9.7    | SYNC DETECTOR                       | 9      |

| 9.7.1  | Normal Operation                    | 10     |

| 9.7.1. | 1 Frame Sync Separator              | 11     |

| 9.7.1. | .2 Multiplex Detector               | 11     |

| 9.7.1. | .3 Sync Interrupt                   | 13     |

| 9.7.2  | Operation in Back-up Mode           | 13     |

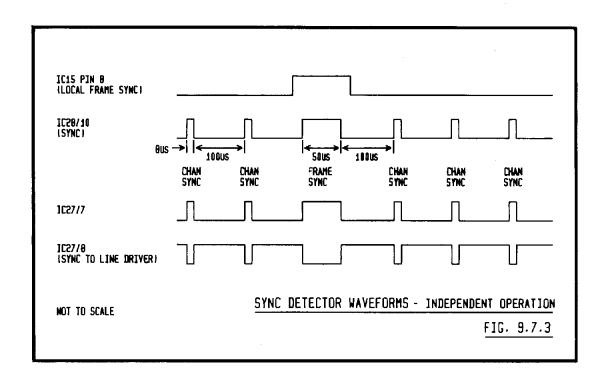

| 9.7.2. | .1 Sync Generator                   | 14     |

| 9.7.2. | .2 Local Frame Sync                 | 14     |

| 9.7.2  | .3 Entering Back-up Mode            | 15     |

| 9.8    | CHANNEL 'ON' DETECTOR               | 16     |

| 0.0    | DECEM CIDCUIT                       | 16     |

# CHAPTER 10 - SERVICING AND MAINTENANCE

| 10.1    | INTRODUCTION                            | 1   |

|---------|-----------------------------------------|-----|

| 10.1.1  | Equipment Required                      | 1   |

| 10.1.2  | General Cautions                        | 2   |

| 10.1.2. | l Power                                 | 2   |

| 10.1.2. | 2 Proms                                 | 2   |

| 10.1.2. | 3 Printed Circuit Boards                | 2   |

| 10.1.2. | 4 Handling CMOS Integrated Circuits     | 2   |

| 10.1.2. | 5 Food and Drink                        | 3   |

| 10.1.2. | 6 Control Panels                        | 3   |

| 10.2    | INITIAL SETTING-UP                      | 3   |

| 10.2.1  | Panel Board (Ref. 1833)                 | . 4 |

| 10.2.2  | Motherboard (Ref. 1832)                 | 4   |

| 10.2.3  | Wheel Interface Board (Ref. 1706)       | 6   |

| 10.2.4  | Video Interface (Ref. 1834)             | 6   |

| 10.2.5  | Console and M24Fx Power Supply Units    | 7   |

| 10.2.6  | Multiplex/Demultiplex Board (Ref. 1828) | 7   |

| 10.2.7  | Effects Processor Board (Ref. 1857)     | 8   |

| 10.3    | ROUTINE SERVICING                       | 9   |

| 10.3.1  | Weekly                                  | 10  |

| 10.3.2  | Quarterly                               | 10  |

| 10.3.3  | Yearly                                  | 10  |

| 10.4    | POWER SUPPLIES                          | 11  |

| 10.4.2  | Fuses                                   | 12  |

| 10.4.2. | l Control Console                       | 12  |

| 10.4.2. | 2 Multiplex Interface Unit              | 12  |

| 10.4.2. | .3 M24Fx                                | 12  |

| 10.5    | REMOVAL AND REFITTING OF SUB-ASSEMBLIES | 12  |

| 10.5.1  | Control Console                         | 13  |

| 10.5.1. | .1 Preliminary                          | 13  |

| 10.5.1. | 2 Power Supply Unit                     | 13  |

| 10.5.1. | 3 Video Interface                       | 13  |

| 10.5.1. | 4 Motherboard                           | 14  |

| 10.5.1. | 5 Panel Board                           | 15  |

| 10.5.1. | 6 Channel Control Wheel                 | 16  |

| 10.5.2  | Multiplex Interface Unit                | 16  |

| 10.5.3  | M24Fx                                   | 16  |

| M24M00                                | Page |

|---------------------------------------|------|

| ag 5 2 a Bullininum                   | 16   |

| 10.5.3.1 Preliminary                  |      |

| 10.5.3.2 Power Supply Unit            | 18   |

| 10.5.3.3 Panel Board                  | 18   |

| 10.6 TEST PROGRAMS                    | 18   |

| 10.6.1 Power-up Self Tests            | 19   |

| 10.6.2 Panel Tests                    | 19   |

| 10.6.2.1 Test 1 - Display Test        | 20   |

| 10.6.2.2 Test 2 - Contact Test        | 20   |

| 10.6.2.3 Test 3 - Communication Test  | 20   |

| 10.6.2.4 Test 4 - Program Test        | 21   |

| 10.6.2.5 Test 5 - Select System Tests | 21   |

| 10.6.3 System Tests                   | 22   |

| 10.6.3.1 VDU Test (A)                 | 23   |

| 10.6.3.2 VDU Test (B)                 | 23   |

| 10.6.3.3 Master and Time Faders       | 24   |

| 10.6.3.4 Tape Interface               | 25   |

| 10.6.3.5 Program Checksum             | 25   |

| 10.6.3.6 Cue Store                    | 25   |

| 10.6.3.7 Analogue Interface           | 26   |

| 10.6.4 Returning to Normal Operation  | 26   |

83Ø8

# DRAWINGS

| 7B26998 | Issue C | Desk Wiring Diagram                         |          |

|---------|---------|---------------------------------------------|----------|

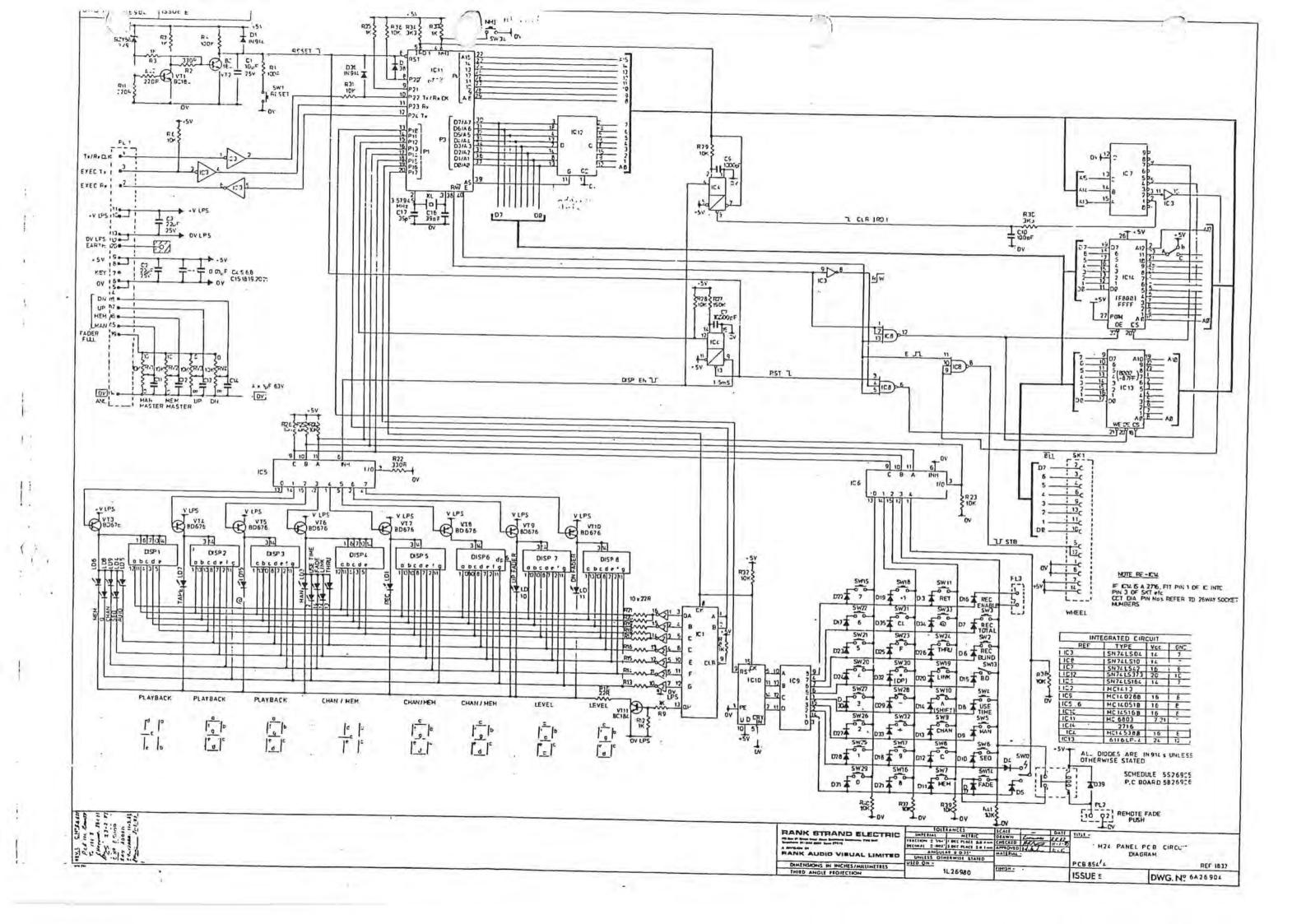

| 6A26904 | Issue E | Panel Board, circuit diagram                | Ref.1833 |

| 6B2431Ø | Issue 3 | Wheel Interface, circuit diagram            | Ref.1706 |

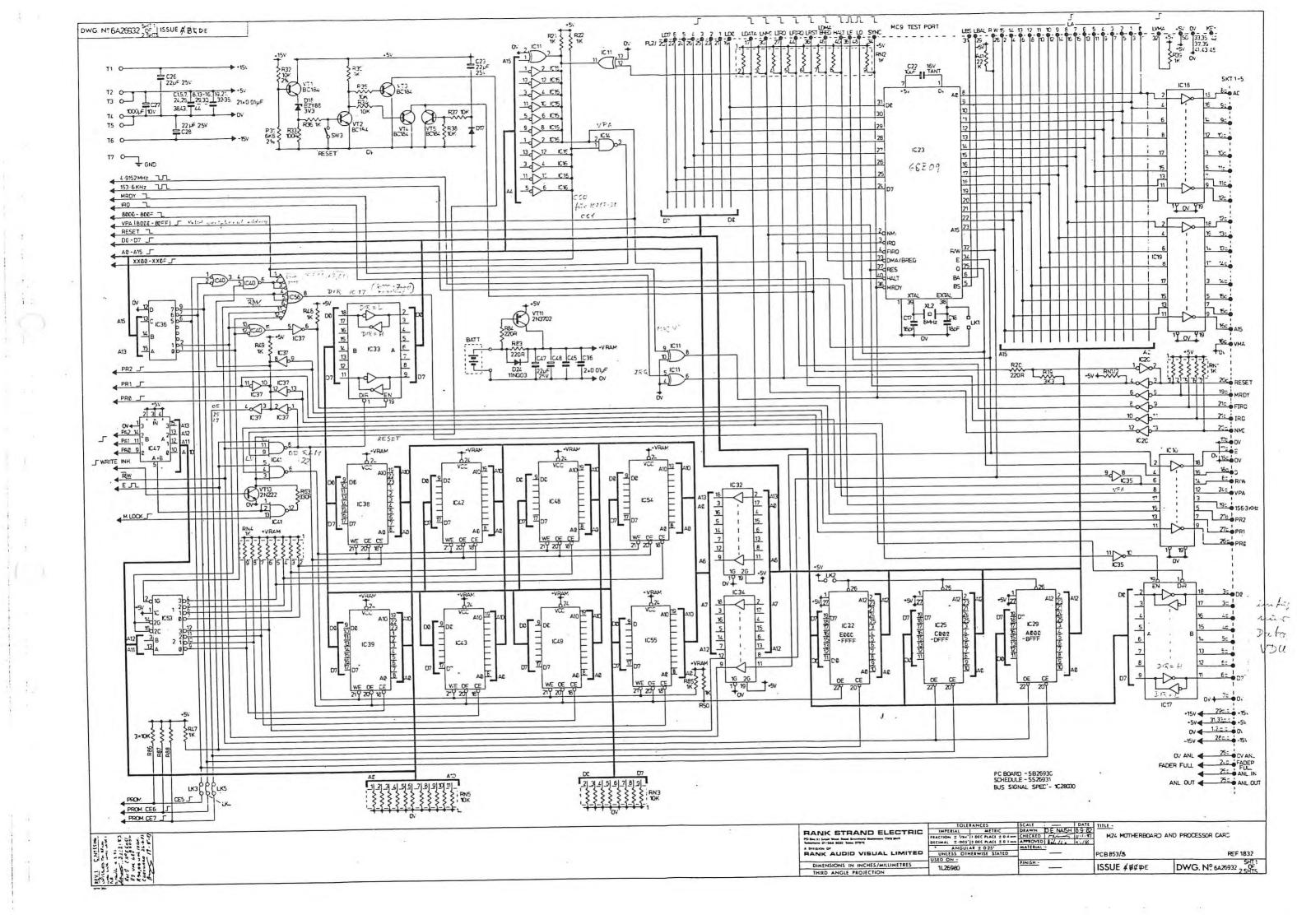

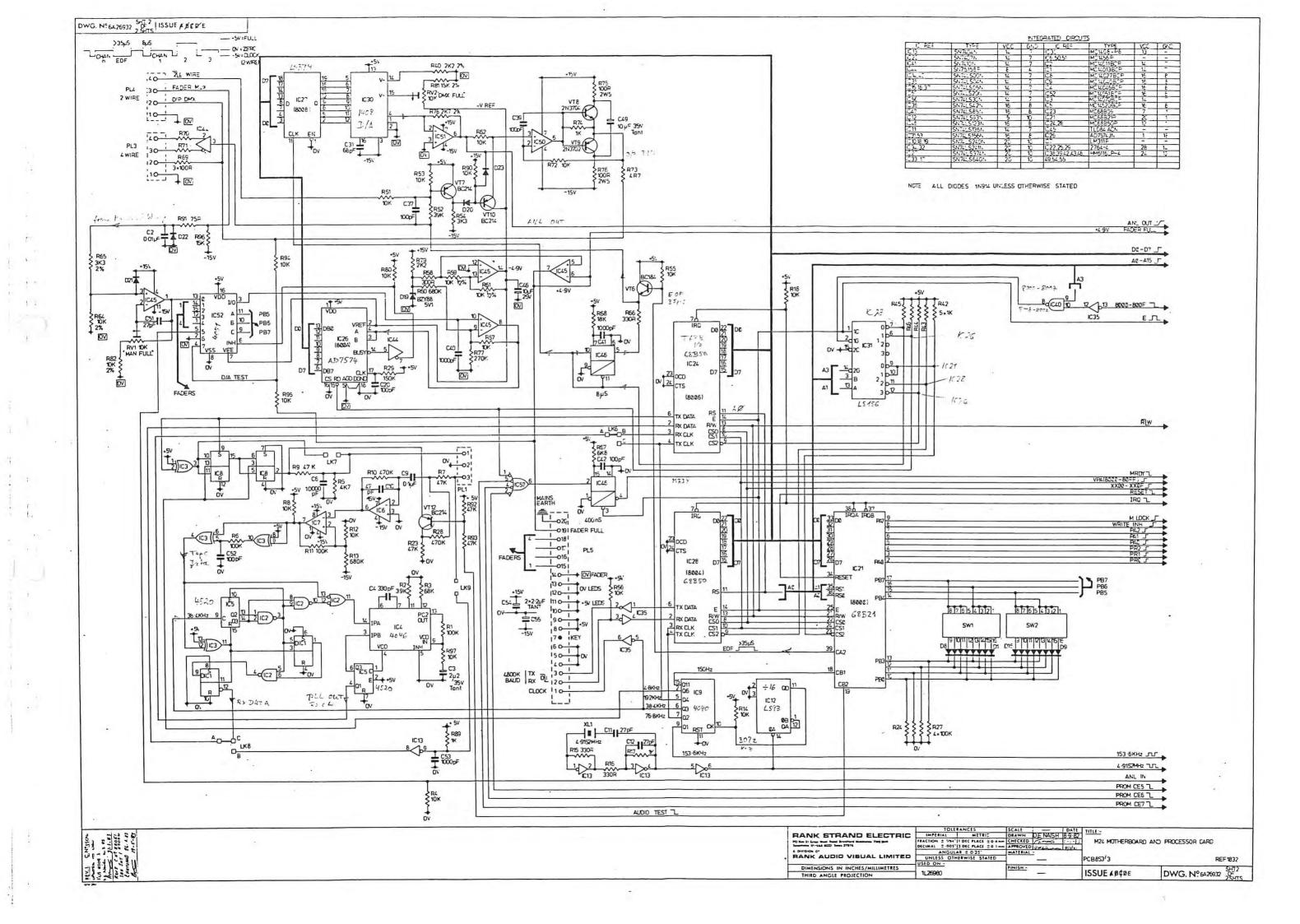

| 6A26932 | Issue E | Motherboard, circuit diagram (2 sheets)     | Ref.1832 |

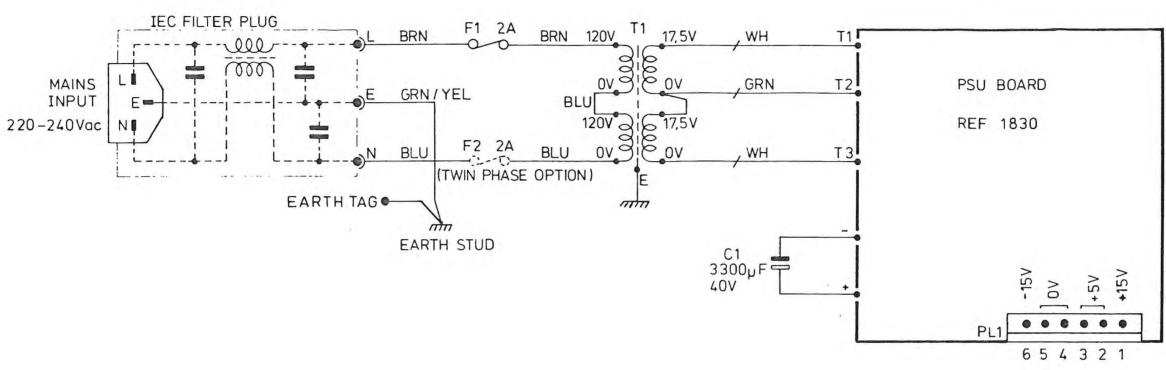

| 7C26933 | Issue B | Power Supply Unit, wiring diagram           |          |

| 6C26865 | Issue D | Power Supply Board, circuit diagram         | Ref.1830 |

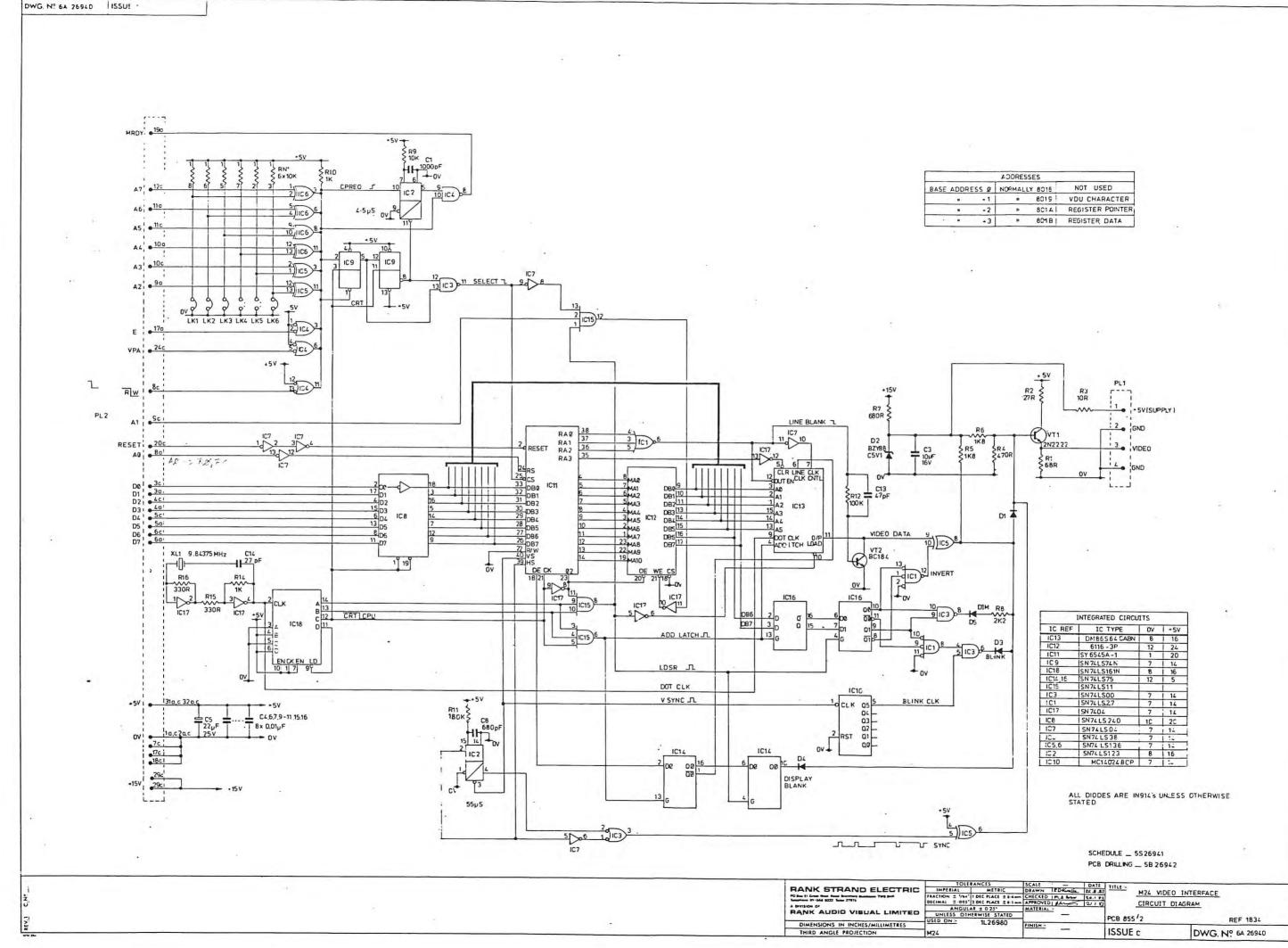

| 6A26940 | Issue C | Video Interface, circuit diagram            | Ref.1834 |

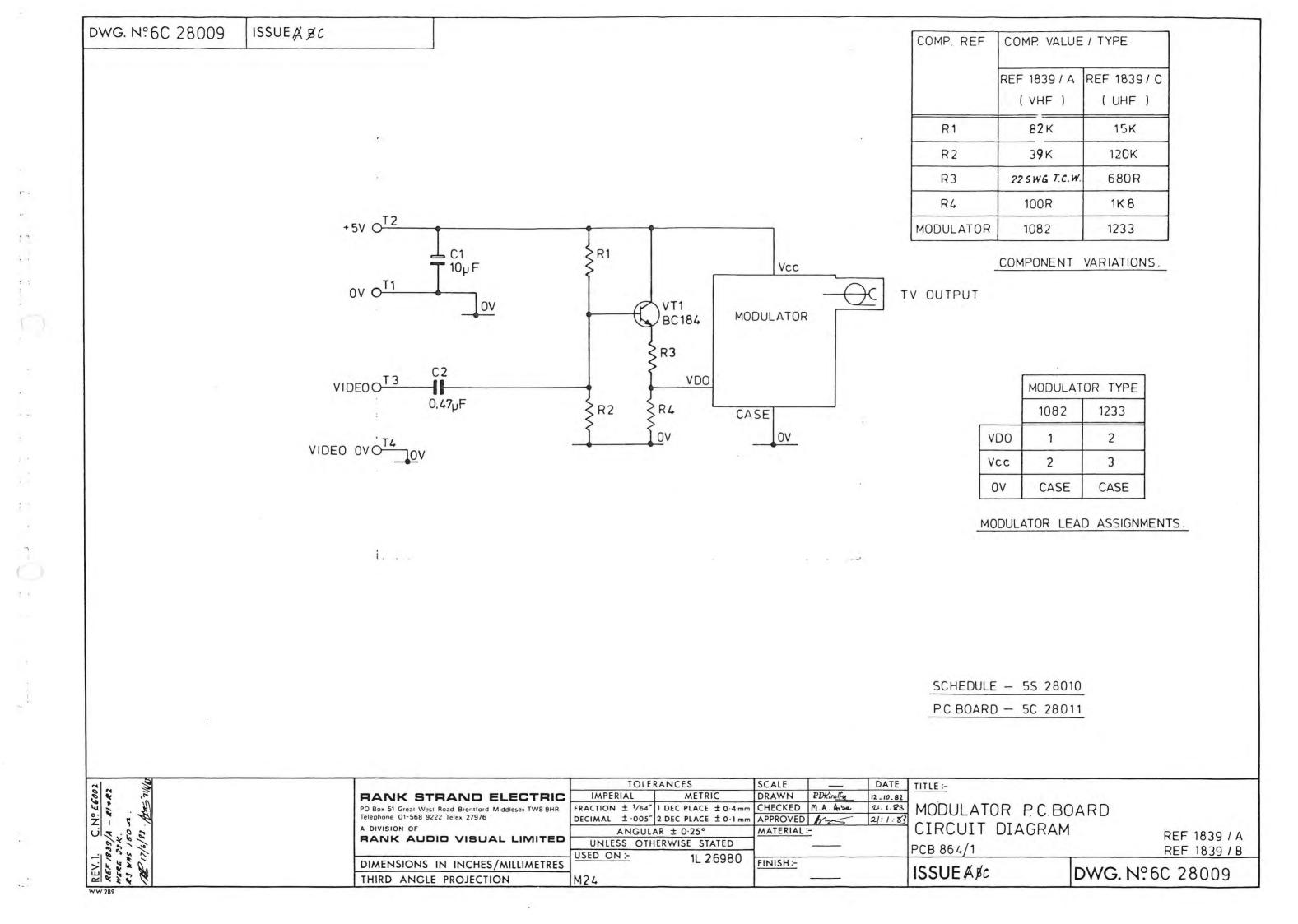

| 6C28ØØ9 | Issue C | Modulator Board, circuit diagram            | Ref.1839 |

|         |         |                                             |          |

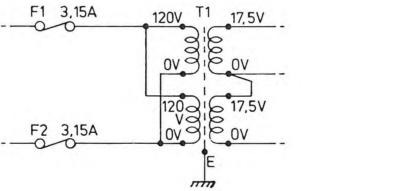

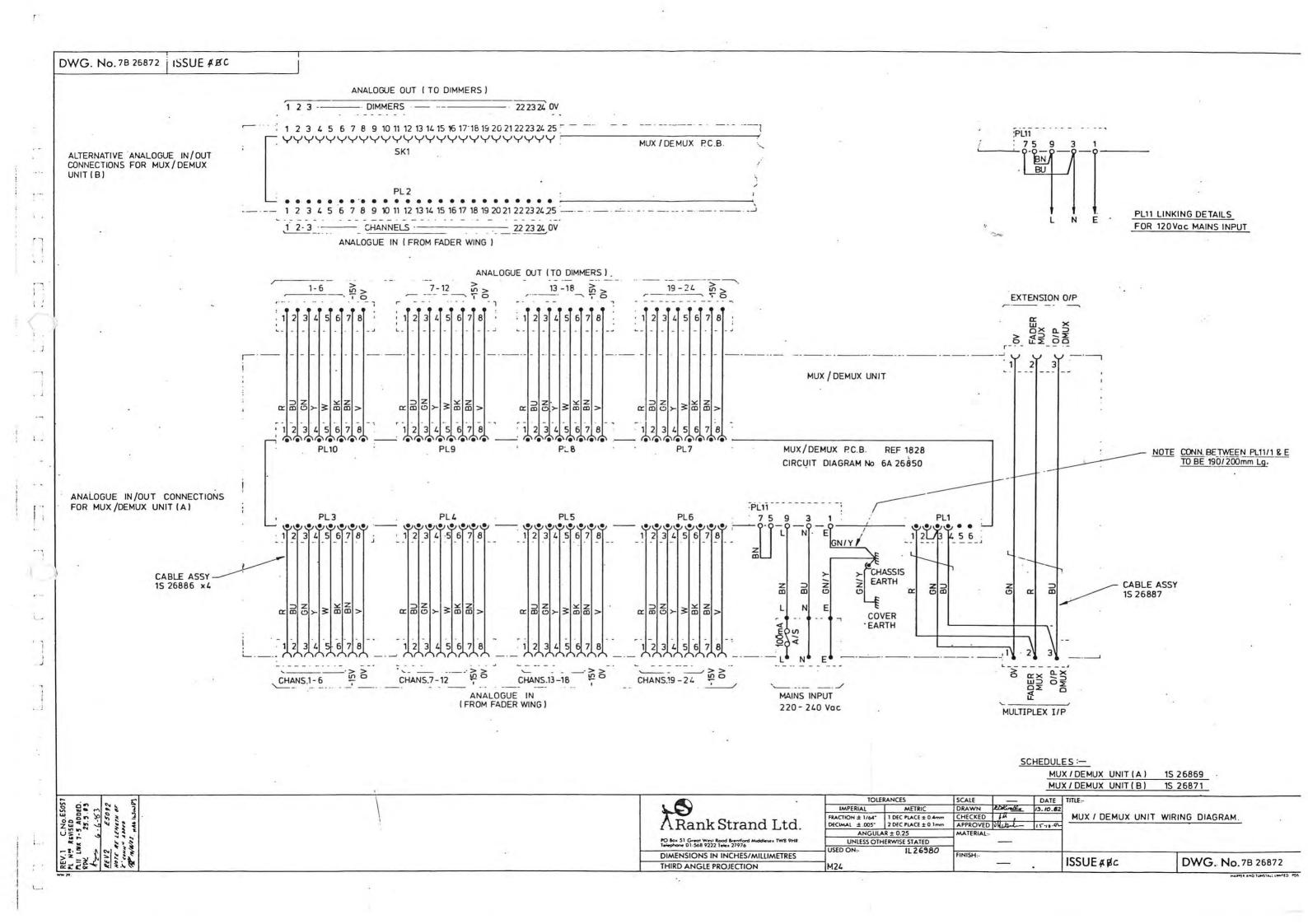

| 7B26872 | Issue C | Multiplex Interface Unit, wiring diagram    |          |

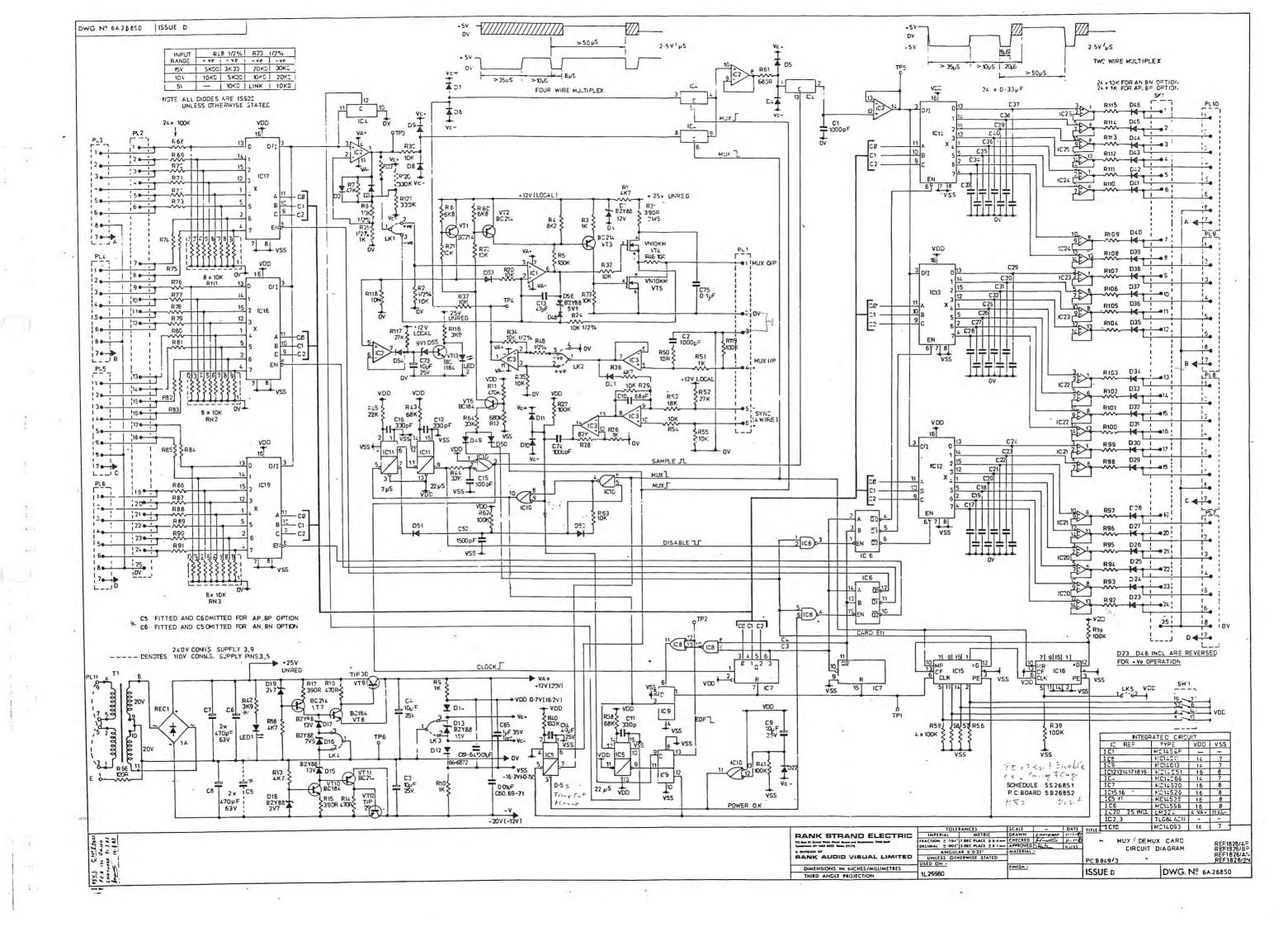

| 6A2685Ø | Issue D | Mux/Demux Board, circuit diagram            | Ref.1828 |

|         |         |                                             |          |

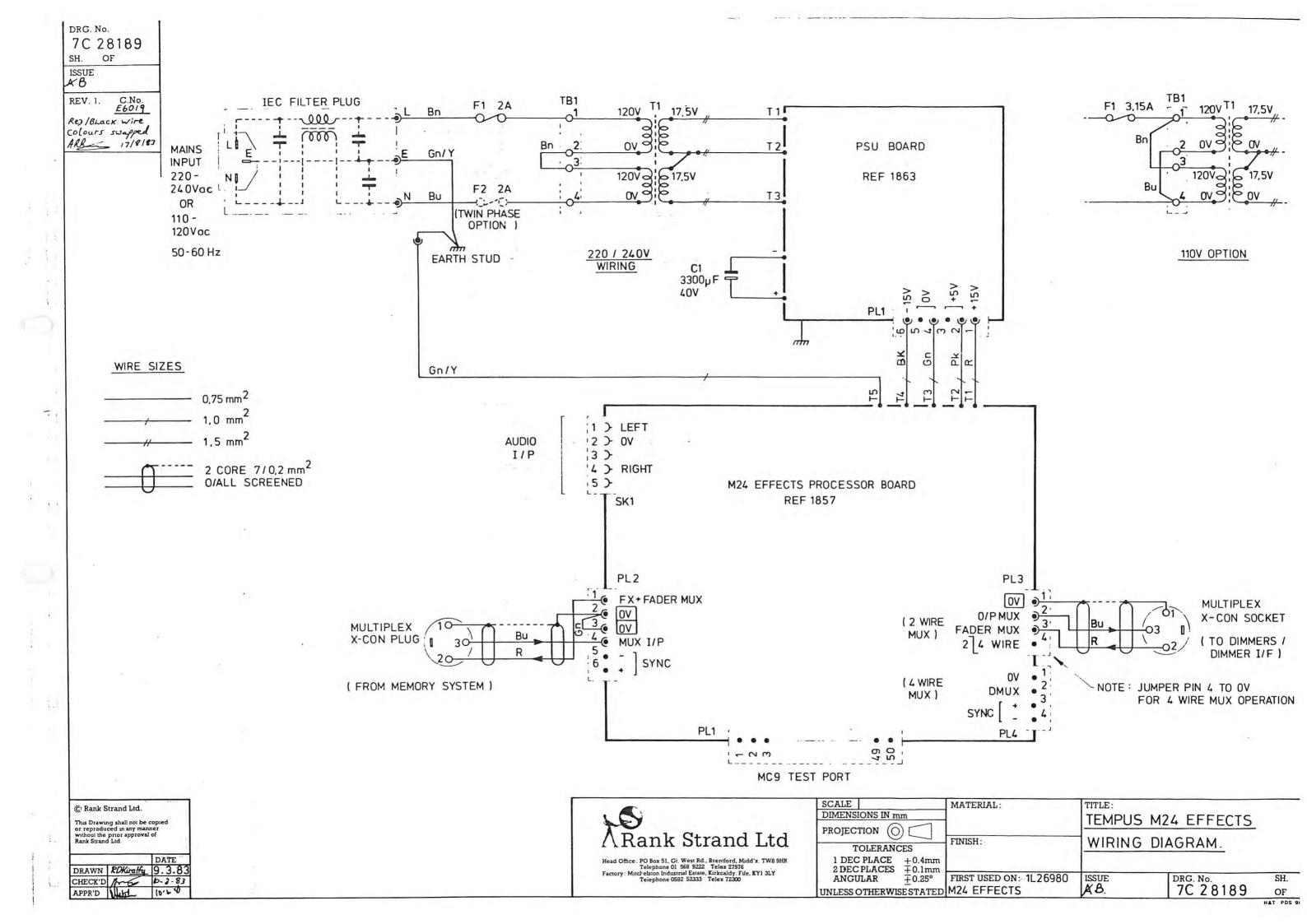

| 7C28189 | Issue B | M24Fx Wiring Diagram                        |          |

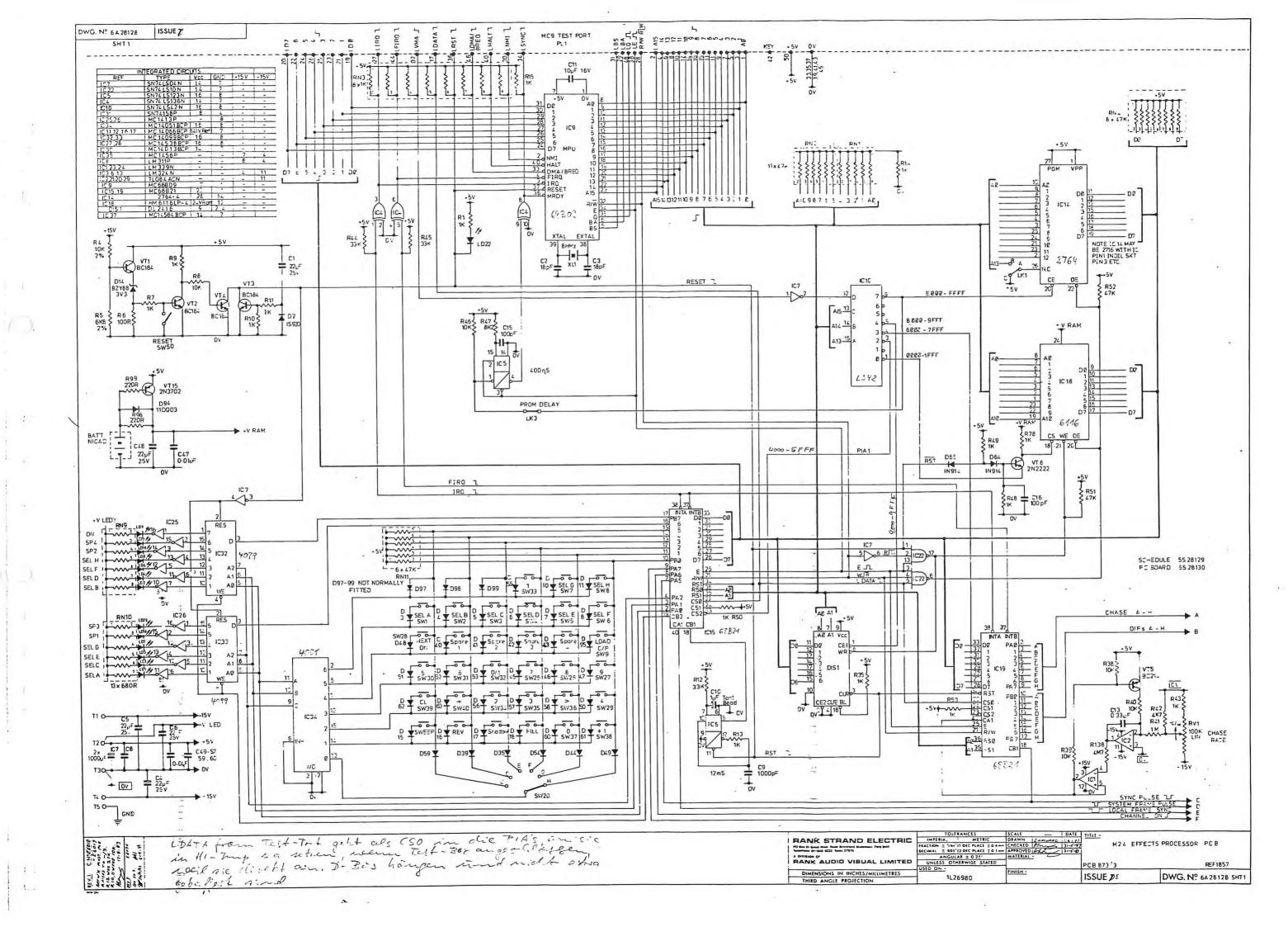

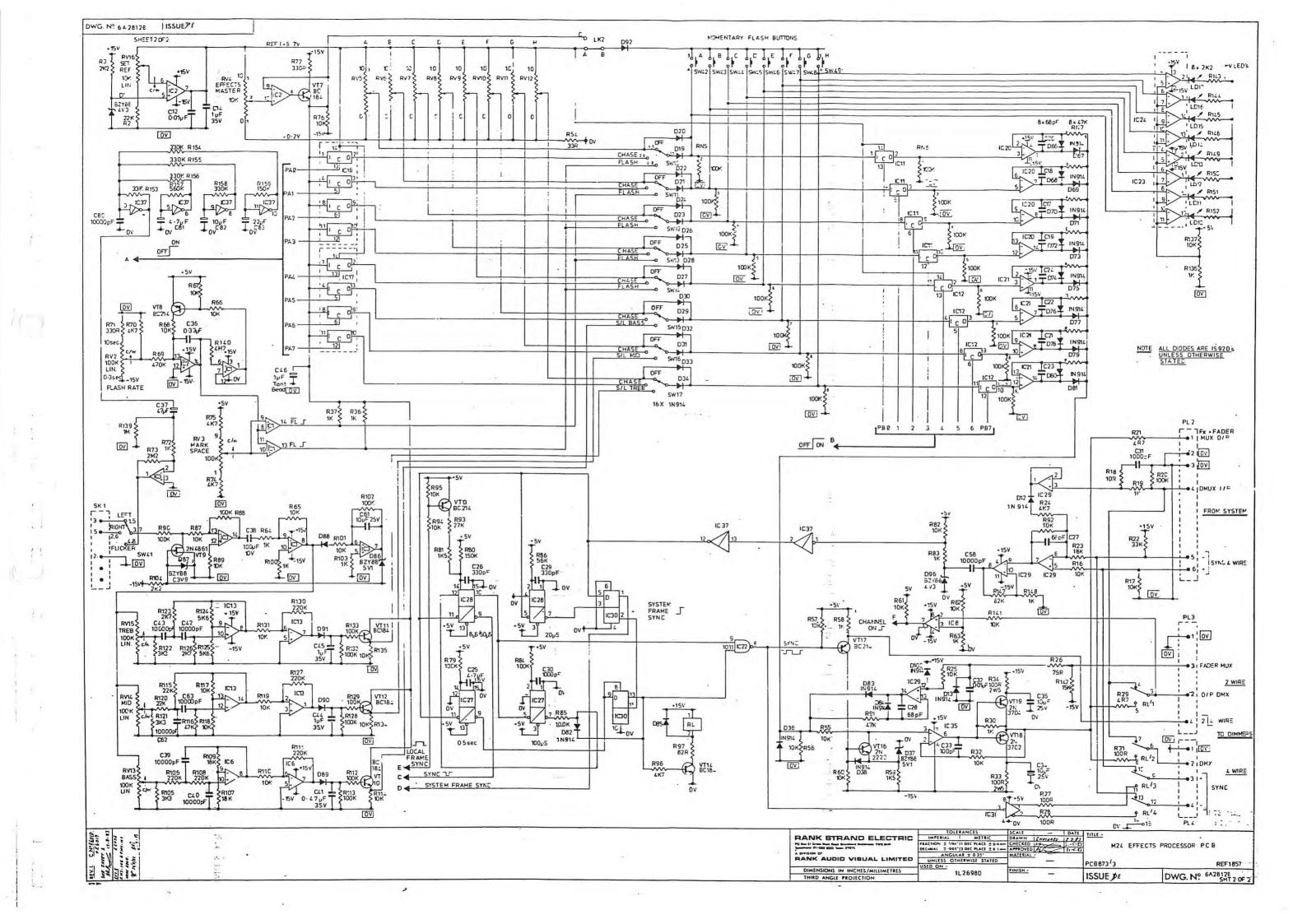

| 6A28128 | Issue E | Effects Processor Board, cct. dia. (2 shts) | Ref.1857 |

| 6C28178 | Issue A | Power Supply Board, circuit diagram         | Ref.1863 |

Issue 1

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 GENERAL

Tempus M24 is a new, compact, memory lighting control system which is intended for use in installations which would previously have been served by a manual system. It offers many of the sophisticated facilities previously available only on much more expensive systems and has an added advantage in that it often may be incorporated in an existing manual system with the minimum of rewiring.

The basic system consists of two units: a Control Console and a 24-way Multiplex Interface unit which produces the dimmer control signals. Additional Multiplex Interface units may be added for systems with more than 24 lighting channels.

In addition to producing dimmer control outputs, the Multiplex Interface unit may accept inputs from another lighting control system, e.g. a Tempus or AMC desk. The contribution from the second system combines with the M24 output on a 'Highest-takes-precedence' basis and may be controlled by a MANUAL master on the M24 console and recorded in the M24 memories.

The number of memories available depends on the number of lighting channels, but this only affects full size, 60-channel systems which have 185 memories. Systems with fewer channels, i.e. 48, 36, 24 and 12, all have 199 memories, the maximum which can be selected on the keypad.

M24 uses battery-maintained electronic memories which will retain their data for at least a week if the system is not used. For longer term storage, the memories may be copied onto tape; most domestic cassette recorders are suitable.

A normal addition to the basic system is the Video Interface, which augments the desk indicators, etc. by producing a comprehensive

'system status' display on a standard monochrome television (not usually supplied by Rank Strand) or a video monitor. The information shown includes the current output levels of all channels, channels currently under control and fade progress.

#### 1.1.1 Patch/Effects System

M24Fx, a simple, independently powered control system with an electronic on/off memory, is available to act as a back-up to M24. The unit includes a special effects system and it can also provide a convenient means of controlling practical circuits and working lights.

#### 1.2 CONSTRUCTION

#### 1.2.1 Control Console

The M24 Control Console is a desk-top unit with a removable lid, which houses the control panel and most of the system electronics. It requires a mains supply of 220/240V or 110/120V a.c. single phase (L. N. and E.), which connects via an I.E.C. 3-pin plug at the rear of the desk. Other connections are as follows:

- i) Data link to the Multiplex Interface unit(s). Two core 0.5mm<sup>2</sup> cable with overall screen, fitted with 3-pin type XLR connectors.

- ii) Connection to a tape recorder (if required). A 5-pin 180° DIN socket is provided adjacent to the Multiplexed Output connector at the rear of the desk.

- iii) Output to Video Mimic. Systems provided with this optional facility have an additional connector panel at the rear of the desk. Two outputs are provided: a UHF signal to drive a standard monochrome television set (VHF is available to special order) and a composite video output for use if a video monitor is available. The television output appears on a standard co-axial connector, and the video on a 75 Ohm BNC connector.

Issue 1 8308

The Control Console houses two main printed circuit boards, the Panel board (Ref. 1833) and the Motherboard (Ref. 1832). These are mounted one behind the other at the rear of the control panel. The Panel board carries the panel controls (with the exception of the channel control wheel) and is responsible for scanning the push-buttons and displays. The Motherboard is responsible for the overall control of the system and for communication with the Multiplex Interface units and the tape recorder.

Other printed circuit boards are as follows:

- i) Power Supply board (Ref. 1830) this forms part of the power supply assembly in the base of the console.

- ii) Wheel Interface (Ref. 1706) this forms part of the channel control wheel assembly on the right of the control panel.

- iii) Video Interface (Ref. 1834), when fitted this is a plug-in 'daughter' board which connects directly onto the Motherboard.

- iv) Modulator board (Ref. 1839), when fitted this board forms part of the Video connector panel at the rear of the console.

# 1.2.2 Multiplex Interface Unit

This is a small unit which may be placed in any convenient position. Two types are available: one intended for use with Tempus dimmer packs and control desks, and the other for use with other types of equipment (e.g. Permus dimmers and AMC control desks). Each unit provides control outputs for 24 dimmers. In installations with more than 24 lighting channels, the Multiplex Interface Units link together, so that only a single connection is necessary from the Control Console.

Issue 1

Page 1 - 4 M24MØ1

#### 1.2.2.1 Connections

Each Multiplex Interface unit requires a mains input of 220/240V or 110/120V a.c. single phase (L. N. and E.), which connects via an I.E.C. 3-pin plug.

The data link from the Control Console connects to a three-pin XLR plug. If more than one Interface unit is used, they link together by connecting the Multiplex Output (EXTENSION O/P) socket on one unit to the MULTIPLEX I/P plug on the next.

The units for use with Tempus dimmers and control desks are fitted with four control cable tails, one for each group of six channels (i.e. 1-6, 7-12, etc.). Each cable is fitted with the necessary 8-pin in-line plug for connection to a Tempus dimmer pack. The control cable for the corresponding channels on the Tempus desk plugs into an 8-pin chassis-mounted socket above and to the left of each cable outlet.

The other type of unit has two chassis-mounted 25-way miniature D-type connectors; a socket labelled OUTPUT 1-24 and a plug labelled INPUT 1-24 for connection to the dimmers and the manual desk respectively.

#### 1.2.3 M24Fx Patch/Effects Unit

The Tempus M24Fx Patch/Effects system is an optional addition to the Tempus M24 Memory Lighting Control. It is designed to fulfil several functions: it can act as a back-up to M24, providing simple control facilities which permit continued operation in the unlikely event of failure of the main console; it provides a suitable means of controlling house-lights, orchestra-lights, etc., for which it may be inconvenient to use the main console; and it includes an effects system which may be used for discotheques, light entertainment, etc.

Issue 1 8308

#### 1.2.3.1 Connections

M24Fx is a desk-top unit similar to the M24 Console. It requires a mains input of 220/240V or 110/120V a.c. single phase (L. N. and E. - the unit must be earthed), which connects via an I.E.C. 3-pin plug. A suitable mains lead is provided, but this must be fitted with a mains plug by the user.

There are normally also two data connections; to the M24 Console (MEMORY SYSTEM) and to the Multiplex Interface units (DIMMER I/F). Only the DIMMER I/F connection is necessary on systems where there is no M24 console. Both data connections use 3-pin type XLR connectors, a suitable cable 5 metres long being provided with both M24Fx and the M24 console; longer (25 metre) cables are available if required.

#### 1.3 SPECIFICATION

Power input - 220V-240V or 110V-120V, 47-63Hz (specified at time of order). Each unit requires a separate power input.

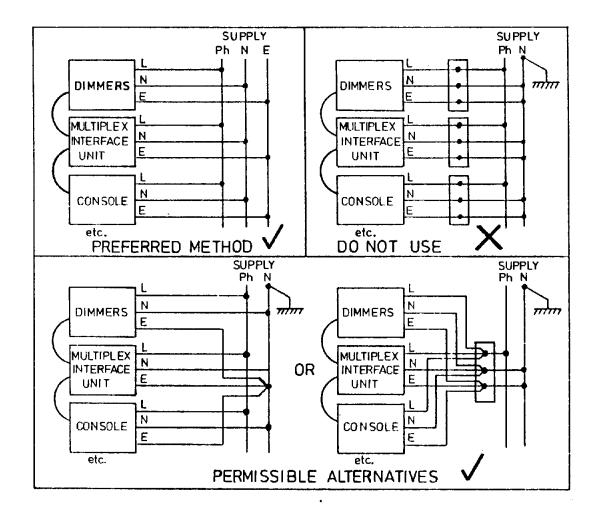

WARNING: Rank Strand Tempus M24 lighting control equipment must be properly earthed if it is to function correctly. IT IS ESSENTIAL THAT EARTH BE AT THE SAME POTENTIAL AT ALL POINTS IN THE SYSTEM. If this is not the case, circulating currents may be generated in the signal earth connections, leading to fluctuating light levels and, in extreme cases, severe damage to the equipment.

In cases where the earth is provided via the supply neutral, all units (i.e. Console, Manual Fader Wing, Multiplex Interface units, Effects unit and dimmers) should ideally be powered from the same source via adequately rated three core (L. N. E.) cable. If this is not possible, a single earth point must be chosen and all the units earthed ONLY AT THIS POINT. The conductors used must be able to carry any potential fault current.

If damage is caused as a result of failure to observe the above recommendations, any warranty will be invalidated. If in doubt, your local Rank Strand agent will be pleased to advise.

8308

Desk output - Multiplexed analogue link via 2-core screened cable.

Dimmer drive outputs (from Multiplexed Interface unit).

- ØV (Off) to -10V (Full) via 10k ohm and silicon äiode.

- Optionally ØV (Off) to +1ØV (Full) via lk ohm and silicon diode.

- Other control voltages are possible, within the limits +/-15V.

Connection is via 4 x 2m long control cables, each terminated in an 8-pin 'Bleecon' plug to mate with Tempus dimmer packs, or via a 25-way 'D' type socket.

Input from Manual Fader Desk or Wing.

- As for dimmer drive outputs.

Connection is via chassis-mounted 8-pin 'Bleecon' sockets to mate with Tempus desks, or via a 25-way 'D' type plug.

Issue 1

#### Control Channels.

In increments of 12, from 24 to 60 maximum. Multiplex Interface unit is required for each 24 channels.

#### Operating Environment.

Temperature,  $\emptyset^{O}C$  to  $35^{O}C$ . Maximum relative humidity, 10% to 90% (non-condensing). 'Office' level cleanliness.

- M6803: 8-bit data, 16-bit address. Processors M68B09: 8-bit data, 16-bit address.

Cycle Time Executive: typically 48ms. Contact scan: typically 12ms.

Fade Processing Accuracy - 16-bit.

Recording Accuracy - 8-bit (256 step).

Output Accuracy - 8-bit (256 step).

#### Fast Access Memory.

- Low-power semiconductor, battery-maintained for a minimum of one week.

- Number of memories available depends on number of channels fitted. 60 channel systems have 185 memories, while smaller systems have 199.

#### Video Mimic Output.

Modulated monochrome UHF (optionally VHF) 625/525 line, 50/60Hz field with connection via co-axial connector, and lV positive composite video with connection via 75 ohm BNC socket.

#### Tape Memory Storage

Uses standard domestic audio recorder. 100mV rms input/output on standard 5-pin DIN socket; mono or stereo.

#### Dimensions - Control Console

53Ømm Width Depth 360mm : 175mm Height : 90mm Clearance required at rear : 235mm Height including lid

: 190mm (depends on OR

position of lid).

- Multiplex Interface Unit

Width : 280mm

Depth : 75mm

Height : 200mm

Clearance required at front : 110mm

#### 1.4 USING THE HANDBOOK

When using this handbook, the following conventions should be noted:

- i) Whenever numbers are used, they are decimal (i.e. to base 10) unless otherwise indicated. Those prefixed with a dollar (\$) sign are hexadecimal (base 16).

- ii) Integrated circuits are identified by their component number, prefixed with the letters IC (e.g. IC7). Where an integrated circuit contains more than one logic element, the output pin number of the element concerned is added as a suffix, e.g. IC13/4. In the case of elements with two or more outputs, e.g. bistables, one of the outputs is chosen for identification purposes, depending on the context.

- iii) The term 'pin' is used to identify connections to integrated circuits. Connections to printed circuit boards are referred to as 'board terminal' or simply 'terminal'.

- iv) Logic levels depend on whether the logic concerned is TTL or CMOS. In the case of TTL, >2.4V equals logic 1 and <0.8V logic 0, while CMOS levels are >3.5V for logic 1 and <1.5V for logic 0, unless the rails to the device concerned determine otherwise. Where a signal is low active, this is indicated in the text and on the circuit diagrams.

#### 1.4.1 Glossary of Terms

The following lists abbreviations and mnemonics used in the handbook:

A0 to A15 Address Bus lines (16 bits) - A0 is the least significant bit. In the case of the 6803, A0 - A7 are multiplexed on the Data/Address bus (D0/A0 - D7/A7) and

addresses are valid on the trailing edge of 'AS'. In the case of the 69B09, addresses are valid on the leading edge of 'Q'.

ACIA Asynchronous Communications Interface Adapter.

AS (6803) Address Strobe - see A0 - A15.

BA (68BØ9) Bus Available.

BS (68B09) Bus Status.

CTS Clear to Send.

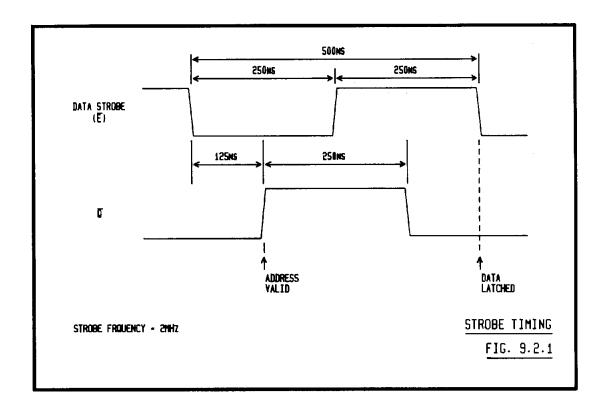

DØ to D7 Data Bus lines (8 bits) - DØ is the least significant bit. In the case of the 6803 these lines also carry multiplexed address signals. For both processors data is valid on the trailing edge of 'E'.

DMA/BREQ Direct Memory Access/Bus Request.

E Phase 2 timing signal - Data is latched on the trailing edge of 'E'. (See also 'Q' and 'AS').

EPROM Erasable Programmable Read only Memory.

FIRQ (68B09) Fast Interrupt Request.

HALT Stop Processing

IRQ Interrupt Request.

LED Light Emitting Diode.

MRDY (68B09) Memory Ready for Transfer - When MRDY is low, 'E' may be stretched, allowing the system to interface with slow memories. The stretch is by integral multiples of quarter clock cycles, up to a maximum of 10 microseconds.

NMI

Non-maskable Interrupt.

PROM

Programmable Read only Memory.

PIA

Peripheral Interface Adapter.

Q (68BØ9)

Quadrature Timing Signal (which leads E) - Addresses from the MPU are valid on the leading edge of 'Q'.

R/W

Read or Write - This signal indicates the direction of data transfer on the Data Bus and is low for Write. It is valid on the rising edge of 'Q' on the 68B09 and on the trailing edge of 'AS' on the 6803.

RESET/RST

Reset Signal - The RESET line is held low during the initial power-on sequence to ensure logical start-up.

RAM

Random Access Memory.

RTS

Request to Send.

Rx

Receiver circuit.

Tx

Transmitter circuit.

#### CHAPTER 2

#### SYSTEMS DESCRIPTION

#### 2.1 INTRODUCTION

This chapter describes the function of the various parts of the system and how they interact. The printed circuit boards are only covered in broad outline. For detailed circuit descriptions see chapters 3-9.

#### 2.2 CONTROL CONSOLE

The Control Console contains two main printed circuit boards: the Motherboard (which carries the Executive processor) and the Panel Board. Smaller boards form part of the Power Supply Unit (in the base of the console) and the channel control wheel. Systems with a Video Mimic have an additional board mounted directly on the Motherboard and a small board carrying the video modulator attached to the video output panel.

The Motherboard and the Panel Board each carry a self-contained microprocessor system. These exchange data by means of a serial link.

#### 2.2.1 Power Supplies

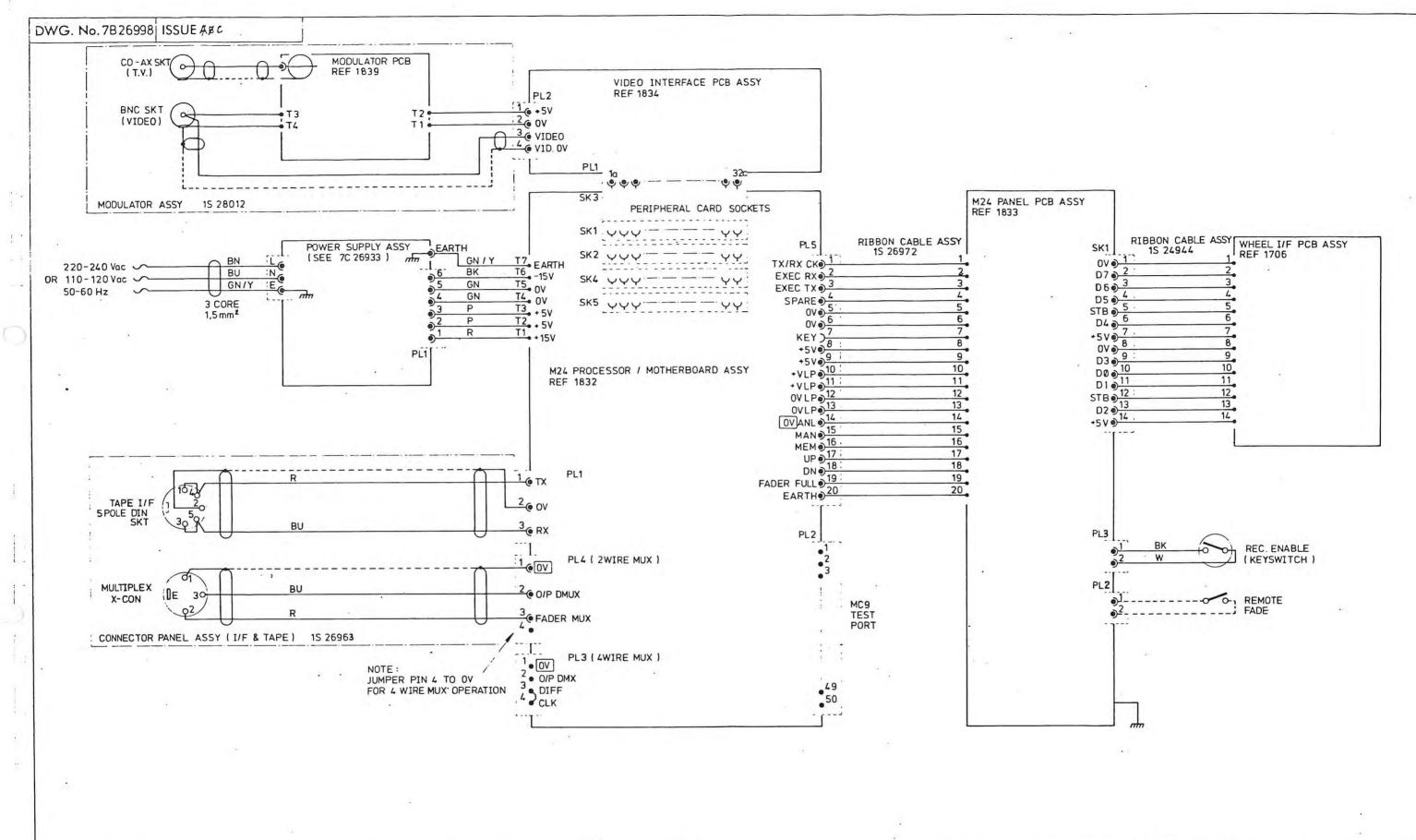

The low voltage power supplies for the Control Console electronics are taken from a single unit mounted in the base of the console. This has outputs at +15V, +5V and -15V, and these are connected to the Motherboard; the latter distributes the power to the other boards as shown on Drawing No. 7B26998.

#### 2.2.2 Panel Board

The Panel Board is mounted on the rear of the control panel and carries the push-buttons, faders and displays. Its microprocessor (M6803) is responsible for scanning the buttons and displays and

also for reading the movement of the fader wheel. It communicates with the Motherboard processor via a serial link.

The panel faders, although mounted on the Panel Board, are not scanned by the Panel processor, but are connected directly to an analogue-to-digital converter on the Motherboard.

#### 2.2.2.1 Address Map

The Panel processor address map is shown in Fig. 2.2.1 and described below:

#### i) Program PROM

The Panel Processor program is held in U.V. erasable PROM (normally 2716) located at addresses \$F800 - \$FFFF. Note that addresses \$E000 - \$F7FF are reserved for future program expansion.

#### ii) External RAM

Addresses \$8000 - \$87FF are reserved for a 2Kbyte RAM (6116LP-4); this is not normally fitted.

#### iii) Wheel Interface

The channel control fader wheel is located at addresses \$4000 - \$5FFF; only address \$4000 is normally used. When the MPU reads from this address the result is a two complement value representing the direction and extent of wheel movement since the last read action.

#### iv) Interrupt Latch

The Panel Processor receives an Interrupt Request about every 1.5ms, from a latch which is set by a signal which enables the display drivers. When the MPU responds to this request, it resets the latch by writing to one of addresses \$2000 - \$3FFF; \$2000 is normally used.

Issue 1 8308

| \$FFFF           |                                  |

|------------------|----------------------------------|

|                  | Program PROM                     |

| \$F8ØØ<br>\$F7FF |                                  |

| \$E000<br>\$DFFF | Reserved for PROM expansion      |

| \$A000<br>\$9FFF | Not Used                         |

| \$8800           | Do Not Use                       |

| \$87FF<br>\$8000 | External RAM (not normally used) |

| \$7FFF           | Not Used                         |

| \$6000<br>\$5FFF | Wheel Interface                  |

| \$4000<br>\$3FFF | Wheel interface                  |

| \$2000<br>\$1FFF | Interrupt Latch                  |

| \$0100           | Not Used                         |

| \$00FF<br>\$0080 | Internal RAM                     |

| \$007F           | Not Used                         |

| \$0020<br>\$001F | Do Not Use                       |

| \$0014<br>\$0013 |                                  |

| \$0010<br>\$000F | Serial Communications Interface  |

| \$0008           | Timer (do not use)               |

| \$0007<br>\$0004 | Not Used                         |

| \$ØØØ3<br>\$ØØØØ | Parallel Interface Port          |

PANEL PROCESSOR ADDRESS MAP Fig. 2.2.1

Page 2 - 4 M24M02

#### v) Internal RAM

Temporary data storage is provided by 128 bytes of random access memory (RAM) which forms part of the Panel Processor; the addresses used are \$0080 - \$00FF.

#### vi) Serial Communications Interface

The Panel Processor communicates with the Motherboard Processor via a serial link; this is controlled by a Serial Communications Interface, which forms part of the Panel Processor, and an Asynchronous Communications Interface Adapter (ACIA) on the Motherboard. Data is transmitted at 4800 baud and each data string consists of one Start bit, eight Data bits and one Stop bit. The Serial Communications Interface is located at addresses \$0010 - \$0013.

The communication protocol is described in section 2.2.4.

#### vii) Timer

The Panel Processor includes a programmable timer, located at addresses \$0004 - \$000F, which is not used in this application.

#### viii) Parallel Interface Port

The Panel Processor incorporates an 8-bit parallel interface port which is used to control the panel displays and indicators, and to detect button actions. Two matrices, one formed by the displays and indicators and the other by the buttons, are scanned simultaneously, about once every 12ms. The port registers are accessible via addresses \$0000 - \$0003.

#### 2.2.2.2 Panel Processor Program

The Panel Processor program consists primarily of interrupt routines, the interrupt requests being generated by the Serial Communications Interface and the Interrupt Latch. On completion of

Issue 1 8308

#### 2.2.3 Motherboard and Executive Processor

The Motherboard is fitted behind the Panel Board and its processor (M68BØ9) controls the overall operation of the M24 system. The board includes the Tape Interface and communicates with the Panel Board and the Multiplex Interface units by means of serial links. Five multiway connectors allow additional, 'daughter' boards - in particular, the Video Interface - to be mounted directly onto the Motherboard.

#### 2.2.3.1 Address Map

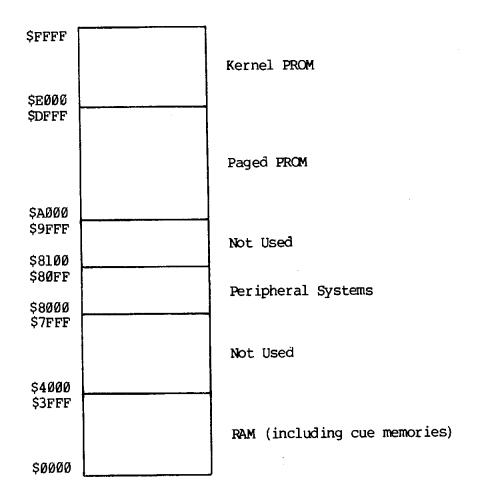

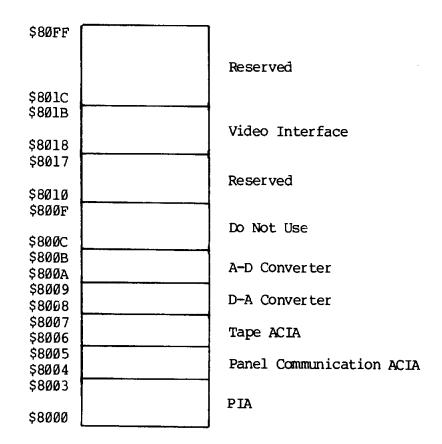

The Motherboard Processor address map is shown in Fig. 2.2.3 and described below:

#### Program PROM

The Motherboard Processor program is held in U.V. erasable PROM (2764) located at addresses \$A000 - \$DFFF (Paged PROM) and \$E000 - \$FFFF (Kernel PROM). In the case of addresses \$A000 - \$DFFF, the PROM on the Motherboard is only one of eight 'pages' selected by a page register (part of the PIA). The other pages are not normally fitted, but if any optional facility requires additional program, the necessary PROMs are incorporated on the appropriate 'daughter' board.

#### ii) Peripheral Systems

Addresses \$8000 - \$80FF are reserved for the various peripheral systems as detailed in Fig. 2.2.4. Those located on the Motherboard have addresses in the range \$8000-F, while the Video Interface (when fitted) occupies addresses \$8010-B.

#### iii) Random Access Memory

The RAM located at addresses \$0000 - \$3FFF provides not only temporary storage for the Motherboard Processor, but also the lighting cue memories. Because of this, it is provided with a battery-maintained supply and may be protected by means of a

8308

MOTHERBOARD PROCESSOR ADDRESS MAP Fig. 2.2.3

memory lock system with a variable threshold. The lock is controlled by the REC LOCK keyswitch on the control panel and the threshold is set so that only the cue memories are protected.

#### 2.2.3.2 Panel Communication Interface

The Motherboard Processor communicates with the Panel Processor by means of an Asynchronous Communications Interface Adapter (ACIA) at addresses \$8004-5. The latter transmits and receives serial data at 4800 baud, the necessary clock signals being produced by a clock generator which also controls the Tape Interface. The data format is one Start bit, eight Data bits and one Stop bit, and the communication protocol is as described in section 2.2.4.

Issue 1

PERIPHERAL ADDRESS AREA Fig. 2.2.4

#### 2.2.3.3 Tape Interface

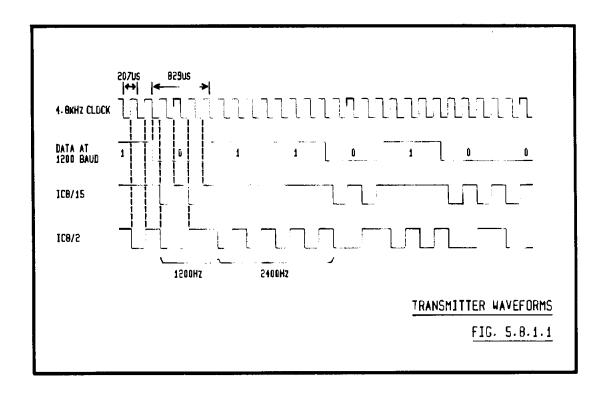

A second ACIA at addresses \$8006-7 provides an interface with a cassette tape recorder the provision of which permits long-term storage of lighting cues. Data is transmitted and received in a CUTS format at 1200 band. The transmission rate is determined by the clock generator mentioned in the previous section, while the receive clock signals are derived from the incoming data by means of an edge detector and a phase-locked-loop.

#### 2.2.3.4 Analogue Interface

The Analogue Interface consists of a digital-to-analogue converter, which generates the multiplexed signal transmitted to the Multiplex Interface units, and an analogue-to-digital converter, which

receives the multiplexed 'Manual Fader Wing' signal from the Multiplexed Interface units and also the outputs from the four faders on the Panel board.

Two types of analogue output are possible: a two-wire system where the multiplexed analogue signal carries channel and frame sync pulses; and a four-wire system where the sync pulses are transmitted separately on a balanced line. In the latter case it is not possible to receive a multiplexed input from a manual fader wing.

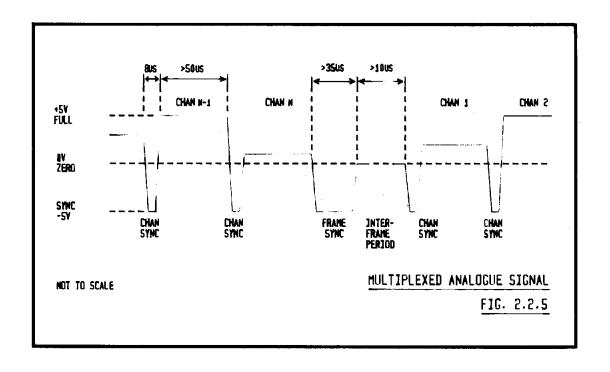

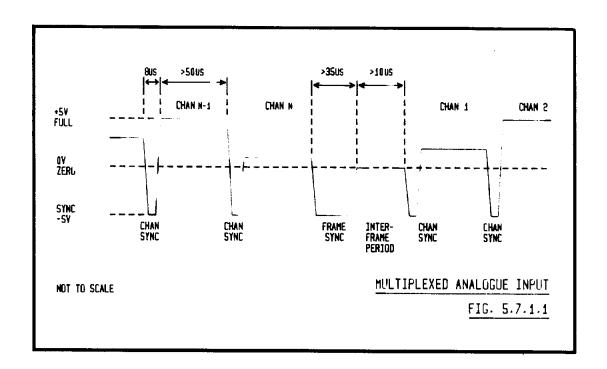

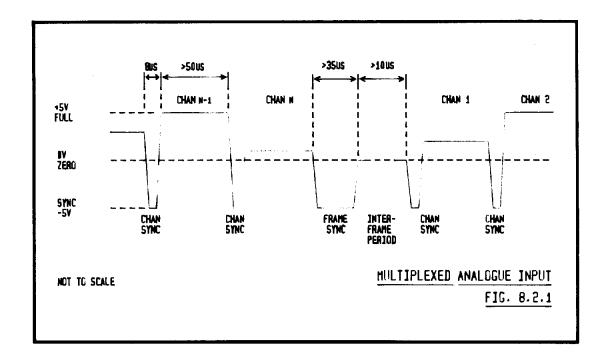

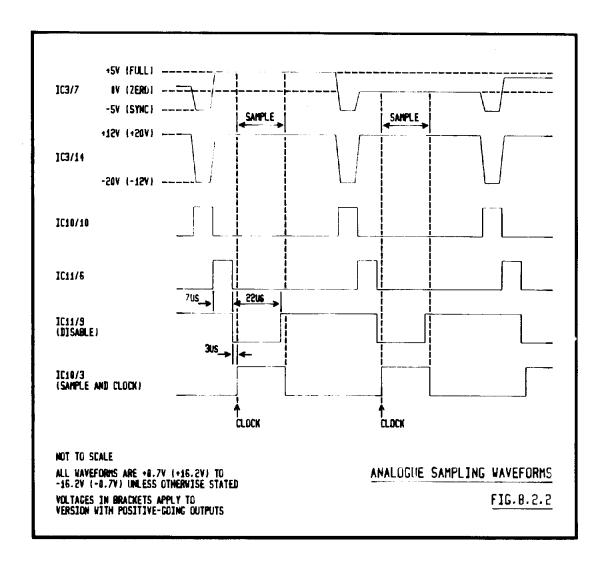

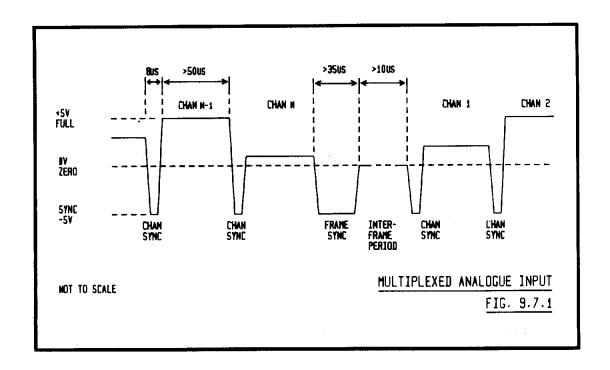

Channel level data is written, in digital form, to a latch at addresses \$8008-9 (\$8008 is normally used). The latch outputs are applied to a digital-to-analogue converter and the analogue channel-level signal is routed to the output via a line driver circuit. The write action also triggers a monostable which produces a negative-going Channel Sync pulse; in the case of the two wire system, the latter overrides the analogue channel-level signal. At the end of each 'frame' of channels, a Frame Sync pulse is produced by the PIA. The form and timing of the two-wire multiplexed analogue signal is shown in Fig. 2.2.5; the four-wire signal is similar, but does not have the negative-going sync pulses superimposed upon it, these being transmitted separately.

Issue 1 83Ø8

The incoming 'Manual Fader Wing' signal from the Multiplex Interface units is applied to an analogue data selector, the other inputs to which are the four fader outputs from the Panel board (see section 2.2.2). The select inputs to this data selector are produced by the PIA. The selected output is stored on a capacitor and this stored level is applied to an analogue-to-digital converter controlled by the Motherboard Processor. When the conversion process is started by the MPU, the data selector is inhibited to prevent any change in the stored level. The conversion then takes place automatically and 15us later the result is read by the MPU via addresses \$800A or \$800B (\$800A is normally used).

#### 2.2.3.5 Motherboard Processor Program

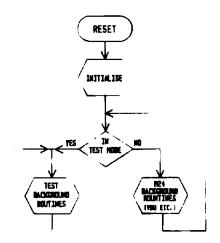

#### a) Power-up

On power-up, the Motherboard Processor first carries out the Power-up Self Tests and then initialises the RAM, ACIAs and PIA. It then reads the system configuration switches, enables interrupts and enters the background loop.

#### b) Background

When no other processing is being carried out, the Motherboard MPU runs in 'background'. Depending on the state of a flag, it will either run the 'Lighting System' background loop, or the 'System Tests' background loop.

The Lighting System background loop is responsible for updating the Video Mimic display and for some of the Tape routines. The System Tests background loop consults various flags which cause the various System Tests to start or stop. All the tests run at background level, and once System Test mode has been selected, it is not possible to return to normal mode without switching the system off.

MOTHERBOARD PROCESSOR PROGRAM

FIG. 2.2.6

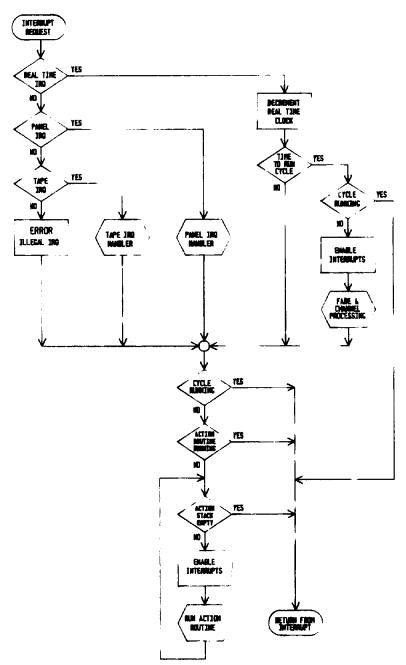

#### c) Interrupts

When an interrupt request is received, the Motherboard Processor determines its source by polling the PIA and ACIAs. It then clears the interrupt flag and enters the appropriate interrupt routine.

Real-time interrupts cause an internal timer to be decremented; this timer controls the routines which deal with fade and channel processing, and with the preparation of mimic updates for transmission to the front panel. All these routines are run on a regular, cyclic basis.

Interrupts generated by the ACIAs cause the appropriate data transfer routines to be carried out. Action routines may also queued if appropriate.

When the interrupt handling is complete, the MPU checks to see whether 'cycle' processing or an Action routine was in progress when the interrupt occurred; if so, it returns to the interrupted routine. If not it checks the Action Stack; if this is empty it returns to background level. If, however, there are actions awaiting, interrupts are enabled and the required Action routines are then carried out, in turn, until the Action Stack is empty. The MPU then returns to background level.

#### 2.2.4 Panel/Motherboard Communication

Communication between the Motherboard and the Panel board is by means of a serial link with a data transmission rate of 4800 Baud. The Serial Communications Interface in the Panel processor and the ACIA on the Motherboard are designed to operate independently of their respective processors and function by generating interrupt requests whenever they have received data or require data for transmission.

#### 2.2.4.1 Communication Format

Data is normally transmitted as Address/Data two byte messages. The Address byte is transmitted first and identifies the button, etc. or display (depending on the direction of transfer) to which the following Data byte refers. Address bytes may have values from \$00 to \$FD, while the values \$FE and \$FF have special meanings which are described below. Data bytes may have any value from \$00 to \$FF.

The Data byte code varies depending on the control with which it is associated, as follows:

#### i) Panel to Motherboard

Buttons and switches - \$80 = On. \$00 = Off.

Wheel - \$80 to \$7F (twos complement).

Positive values represent upward movement and negative downward.

#### ii) Motherboard to Panel

Numeric Displays - BCD code (1 or 2 displays/byte).

Mimic Lamps, etc. - \$00 to \$FF, 1 bit/mimic.

#### 2.2.4.2 Control Bytes

An Address byte with the value \$FF indicates that the byte following should be interpreted as a Control byte rather than a Data byte. Control bytes may have values \$00 to \$0F, \$FC, \$FD and \$FF.

The values \$00 to \$0F are used to select address areas (pages). Because Address bytes can have only 254 unique values, this is the maximum number of buttons/displays which can be identified by an Address/Data pair. The use of sixteen address areas expands the capacity of the system by sixteen times. This capability is not normally used on M24.

Issue 1 8308

The remaining Control byte values have the following meanings:

\$FC - Pause Transmission.

\$FD - Continue Transmission.

\$FF - Requests the current status of all buttons/

displays (as appropriate).

# 2.2.4.3 Sync Byte

In order to ensure that Address and Data bytes are correctly interpreted, the Panel and Motherboard communication systems are synchronised by means of Address byte \$FE. This has no Data byte associated with it and is generated by the Motherboard Processor every 30ms (approx). Whenever the Panel receives this byte, it responds by transmitting the same value to the Motherboard, before the next Address/Data pair. If the Panel does not respond correctly, the Motherboard Processor will recognise that a Sync error has occurred.

If the Panel receive system is not synchronised with the Motherboard, the Sync byte will be interpreted as Data and the next byte, correctly, as an Address. The two systems will thus be re-synchronised. Similarly, if the Motherboard receive system is not in synchronism with the Panel, the two systems will be automatically re-synchronised when the Sync byte is transmitted.

To ensure that the displays remain correct and that the Motherboard is aware of all Panel button actions, etc., whenever a Sync error is detected the Motherboard transmits the Address/Data pair \$FF, \$FF (Request current status) and sends the correct state for all the displays.

#### 2.2.5 Video Interface

The Video Interface is an optional addition to the M24 system and is carried on a small plug-in 'daughter' board. This connects directly to the Motherboard via any one of five 'system bus' connectors. External connections are made via a video connector panel fitted in the rear extrusion of the desk, which incorporates a small board

carrying a UHF (or, in some cases, VHF) modulator; the video mimic may therefore be provided by either a standard monochrome television or, for improved display quality, by a television monitor.

The video interface carries 2Kbytes of Video RAM, a Cathode Ray Tube Controller (CRTC) and a Character Generator. Data loaded into the Video RAM by the Motherboard Processor is retrieved on a cyclic basis by the CRTC and converted into the video signals required by the Video Mimic.

The CRTC (6545) is a programmable device which is initialised by the Motherboard Processor each time the system is powered-up. The screen format consists of 25 lines of 64 characters each, and each character is formed in a 7  $\times$  5 dot matrix. The scan rate is adjusted to be compatible with 50Hz or 60Hz systems (625/525 line respectively) as required, at a basic dot rate of 9.84375MHz.

Each location in the Video RAM corresponds to a particular position on the VDU screen. The Motherboard Processor does not, however, have direct access to the Video RAM, but must load the address of the required screen location into a register in the CRTC. This 'update' address is multiplexed with the video scan addresses so that, as the scan takes place, update and scan addresses alternate. The Motherboard Processor then writes to the Video RAM via address \$8019, the write action being delayed, if necessary, by means of MRDY (see glossary - chapter 1), until the update address location is next selected. The characters loaded into the RAM are in a modified form of upper-case ASCII code (see Table 2.2.1).

Only six bits are necessary to represent the character, the remaining two bits (bits 6 and 7) being used to define the character 'Attribute', as follows:

| DB6 | DB7 | Attribute               |

|-----|-----|-------------------------|

| Ø   | Ø   | Normal Character        |

| 1   | Ø   | Flashing Character      |

| Ø   | 1   | Inverse Video Character |

| 1   | 1   | Dim Character           |

Table 2.2.1

|     |     |     |     |     |   | •       |   |

|-----|-----|-----|-----|-----|---|---------|---|

|     |     |     | DB5 | Ø   | Ø | 1       | 1 |

|     |     |     | DB4 | Ø   | 1 | Ø       | 1 |

|     |     |     |     |     |   |         |   |

| DB3 | DB2 | DB1 | DBØ |     |   |         |   |

|     |     |     |     |     |   |         |   |

| Ø   | Ø   | Ø   | Ø   | @   | P | (Space) | Ø |

| Ø   | Ø   | Ø   | 1   | A   | Q | !       | 1 |

| Ø   | Ø   | 1   | Ø   | В   | R | 11      | 2 |

| Ø   | Ø   | 1   | 1   | С   | S | #       | 3 |

| Ø   | 1   | Ø   | Ø   | D D | т | \$      | 4 |

| Ø   | 1   | Ø   | 1   | Е   | U | 8       | 5 |

| Ø   | 1   | 1   | Ø   | F   | V | &       | 6 |

| Ø   | 1   | 1   | 1   | G   | w | 1       | 7 |

| 1   | Ø   | Ø   | Ø   | н   | х | (       | 8 |

| 1   | Ø   | Ø   | 1   | I   | Y | )       | 9 |

| 1   | Ø   | 1   | Ø   | J   | Z | *       | : |

| 1   | Ø   | 1   | 1   | K   | [ | +       | ; |

| 1   | 1   | Ø   | Ø   | L   | \ | ,       | < |

| 1   | 1   | Ø   | 1   | м   | ] | -       | = |

| 1   | 1   | 1   | Ø   | N   | ^ | •       | > |

| 1   | 1   | 1   | 1   | 0   | _ | /       | ? |

| l   |     |     |     | 1   | 1 |         |   |

As each character is retrieved from the Video RAM by the CRTC, it is applied to a Character Generator integrated circuit, which produces dot signals. These, when displayed on the VDU screen, form the character concerned. The dots are converted to serial form, given the correct attribute and incorporated in a composite video waveform which is applied to the monitor.

The Video Interface is located at addresses \$8018 - \$801B in the Motherboard Processor address map.

Page 2 - 18 M24M02

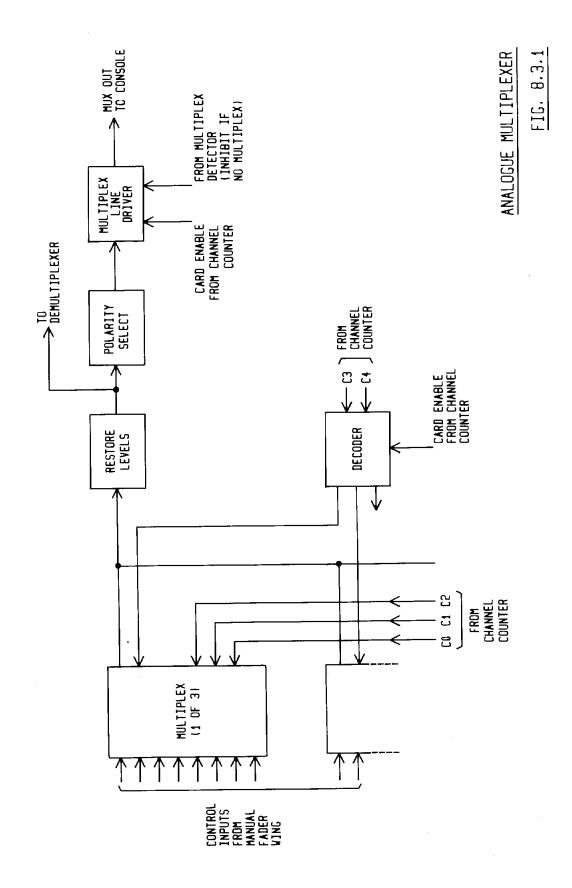

## 2.3 MULTIPLEX INTERFACE UNIT

Each Multiplex Interface unit contains a single Multiplex/Demultiplex board which generates the dimmer drive outputs for 24 lighting channels and receives control inputs from the corresponding channels on the Manual Fader Wing. Each unit is self-contained and independently powered.

Where several Multiplex Interface units are provided these link together via 3-pin XLR connectors; only one connection is therefore necessary from the Control Console. The Manual Fader Wing inputs and dimmer drive outputs are either via 8-pin 'Bleecon' connectors or 25-pin miniature D-type connectors.

# 2.3.1 Channel Demultiplexer

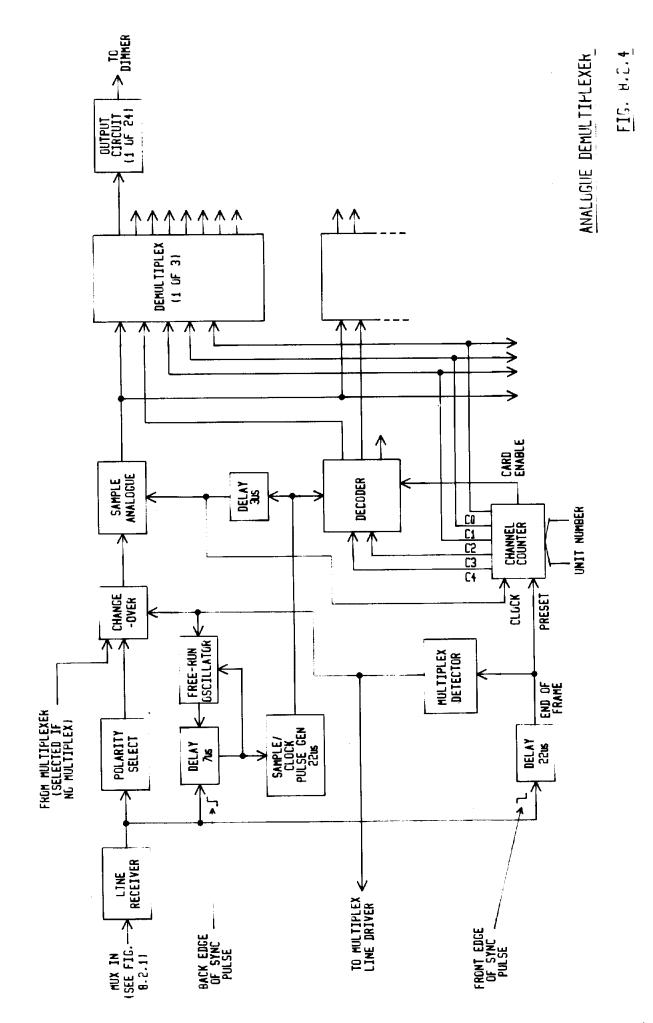

The channel demultiplexer is responsible for sampling the incoming analogue multiplex signal from the Control Console and routing the appropriate lighting channel levels to the dimmer drive outputs.

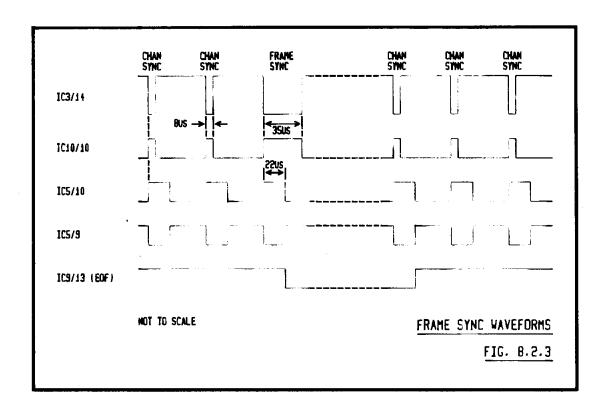

The analogue multiplex signal takes the form shown in Fig. 2.2.5. The lighting channels levels are transmitted serially in numeric order, one complete transmission (frame) of all the channels controlled by the system occurring about every 50ms. At the end of each frame, a channel counter is loaded with a preset value which depends on the group of channels served by the board, i.e. on the setting of the Channel Group Selector below the multiplex When the next frame begins, the Channel Sync pulses connectors. clock the counter and, when a particular counter state established, the board is enabled. This state is the same for all the Multiplex Interface units, but because of the different preset values it occurs at a different time in the frame in each unit. Each unit is therefore enabled only when the levels of the channels it serves are being received.

During the period when the board is enabled, the analogue level is sampled and routed to the appropriate output circuit where it is stored on a capacitor. The required output is selected by the counter.

# 2.3.2 Channel Multiplexer

The Multiplex/Demultiplex board also includes a multiplexer which receives its inputs from the channel control outputs of the Manual Fader Wing. These inputs are selected by the counter in the same way as for the demultiplexer. The multiplexed signal is routed to the Control Console via a line driver circuit.

### 2.3.3 Independent Operation

The unit includes an oscillator which, in the absence of an analogue multiplex signal from the control console, permits the control signals from the Manual Fader Wing to be routed via the multiplexer and the demultiplexer to the dimmer drive outputs. This permits the Manual Fader Wing to be used if the M24 Control Console is inoperative.

#### 2.4 M24Fx PATCH/EFFECTS UNIT

The M24Fx console contains one main printed circuit board (the Effects Processor board) and one smaller board, which forms part of the Power Supply unit.

#### 2.4.1 Power Supplies

The low voltage supplies for the M24Fx electronics are taken from a single unit mounted in the base of the console. This unit has outputs at +15V, +5V and -15V and these are connected to the Effects Processor board as shown in Drawing No. 7C28189.

### 2.4.2 Effects Processor Board

This board is mounted on the rear of the control panel and carries the push-buttons, switches, faders and displays. Its microprocessor (M68BØ9) is responsible for the overall operation of the Patch system and also for generating the Chaser outputs for the Effects system. With the exception of the Chaser, the Effects are not microprocessor controlled, but are provided by dedicated circuits comprising a Flash Generator, a Sound-to-light Generator and momentary Flash buttons.

The board also includes a sync detector/generator by means of which the unit may act as a back-up to the M24 Console.

#### 2.4.2.1 Address Map

The Effects Processor address map is shown in Fig. 2.4.1 and described below:

### i) Program PROM

The Effects Processor program is held in ultra-violet erasable PROM (normally 2716) located at addresses \$F800 - \$FFFF. Note that addresses \$E000 - \$F7FF are reserved for future expansion.

#### ii) Alpha-numeric Display

A four-digit latching alpha-numeric display (keypad display) is located at addresses \$8000 - \$9FFF. This device is write-only and only if fact occupies four addresses, one for each digit; \$8000-3 are normally used.

### iii) Peripheral Interface Adapters

Two Peripheral Interface Adapters (PIAs) are provided at addresses \$4000 - \$5FFF and \$6000 - \$7FFF respectively. The first of these is used to scan the panel push-buttons and indicators and to generate real-time interrupts, while the

| \$FFFF                               |   |                                |

|--------------------------------------|---|--------------------------------|

| 71111                                |   |                                |

|                                      |   | Program PROM                   |

|                                      |   | riogiam riogi                  |

| \$F800                               |   |                                |

|                                      |   |                                |

| \$F7FF                               |   | December for PDOM companies    |

| cnaaa                                |   | Reserved for PROM expansion    |

| \$E000                               |   |                                |

| \$DFFF                               |   |                                |

| <b>+</b> - <b>- - - - - - - - - </b> |   | Not Used                       |

| \$A000                               |   |                                |

| \$9FFF                               |   |                                |

|                                      |   | Do Not Use                     |

| \$8004                               |   |                                |

| \$8003                               |   |                                |

|                                      |   | Alpha-numeric Display          |

| \$8000                               |   |                                |

| \$7FFF                               |   |                                |

|                                      |   | Do Not Use                     |

| \$6004                               |   |                                |

| \$6003                               |   |                                |

|                                      | i | PIA 2                          |

| \$6000                               |   |                                |

| \$5FFF                               |   |                                |

|                                      |   | Do Not Use                     |

| \$4004                               | , |                                |

| \$4003                               |   |                                |

|                                      |   | PIA 1                          |

| \$4000                               |   |                                |

| \$3FFF                               |   |                                |

| •                                    |   | Not Used                       |

| \$2000                               |   |                                |

| \$1FFF                               |   |                                |

| T                                    |   | Do Not Use                     |

| \$0800                               |   | 20 000 000                     |

| \$07FF                               |   |                                |

| 40 11 1                              |   |                                |

|                                      |   | RAM (including Patch memories) |

|                                      |   |                                |

| \$0000                               |   | 1                              |

| 40000                                |   | J                              |

EFFECTS PROCESSOR ADDRESS MAP Fig. 2.4.1

other provides the channel on/off and Chaser outputs. Other lines on both devices are used in connection with the sync detector/generator.

As in the case of the Alpha-numeric Display, the PIAs only occupy four addresses each, \$4000-3 and \$6000-3 being normally used.

# iv) Random Access Memory

The RAM located at addresses \$0000 - \$07FF provides not only temporary storage for the Effects Processor, but also the Patch memories. Because of this, it is provided with a battery-maintained supply.

#### 2.4.2.2 Patch Master Faders

Page 2 - 22

The outputs from each Patch Master fader is routed via the OFF contact of the appropriate OFF/CHASE/FLASH switch to an analogue switch controlled by the Port B outputs of PIA 2. As each channel is scanned, the On/Off states for that channel in the eight patch memories are retrieved from the RAM and determine whether the combination of the master fader and the effects should appear at the output.

The eight Patch Master outputs and the multiplexed Manual Fader Wing signal from the Multiplex Interface units are combined together in a Highest-takes-precedence circuit and routed via a line driver circuit to the M24 Console.

#### 2.4.2.3 Effects System

The automatic effects system comprises a Chaser, a Flash Generator and a Sound-to-light Generator. In addition, a momentary action Flash switch is associated with each of the Patch Master faders.

Issue 1 83Ø8

#### i) Chaser

The chase signals are generated by the MPU in response to interrupts produced, via PIA 2, by an adjustable rate pulse generator. The chase outputs appear on Port B of PIA 2 and these control eight analogue switches. Each of the latter routes the output of the EFFECTS MASTER to the CHASE contact of the corresponding OFF/CHASE/FLASH switch.

### ii) Flash Generator

This consists of an adjustable slope saw-tooth generator, the output of which is compared with the setting of the MARK-SPACE control. There are two comparators, producing non-inverted and inverted flash signals for effects channels A, C and E, and B and F respectively.

#### iii) Sound-to-light Generator

The Sound-to-light Generator consists of an AGC circuit feeding three filters, bass, middle and treble. The output of each filter switches the EFFECTS MASTER output onto the appropriate contact of the corresponding OFF/CHASE/FIASH switch (Patch Masters F, G and H respectively).

The input to the Sound-to-light Generator may be taken from either channel (left or right) of a stereo signal connected via the DIN socket on the control panel. The system is intended to be driven from the pre-amplifier stage of a tape recorder, etc., and the input must not, under any circumstances, exceed 5V peak-to-peak.

As an alternative to the audio input, the Sound-to-light Generator may be driven from a Random Flicker Generator (position F on the L/R/F switch). This consists of four oscillators operating at different frequencies, the outputs of which interact to produce a pseudo-random output.

### 2.4.2.4 Sync Detector

In addition to providing patch and effects facilities, etc. M24Fx can act as a back-up to M24, thus permitting continued operation in the unlikely event of failure of the main console.

In normal operation, the multiplexed Manual Fader Wing signals from the Multiplex Interface units are combined on a highest-takes-precedence basis with the output of M24Fx and routed to the M24 Console, while the output from the M24 Console is routed to the Multiplex Interface units via M24Fx without additional processing. The timing of the operation is controlled by the sync pulses from M24.

If for any reason the sync pulses from the M24 Console cease, a relay will change over, routing the combined Manual Fader Wing and M24Fx signals to the Multiplex Interface units, and M24Fx will generate sync pulses. These sync pulses will be superimposed on the multiplexed analogue output or transmitted separately, depending on whether the system in use is two-wire or four-wire.

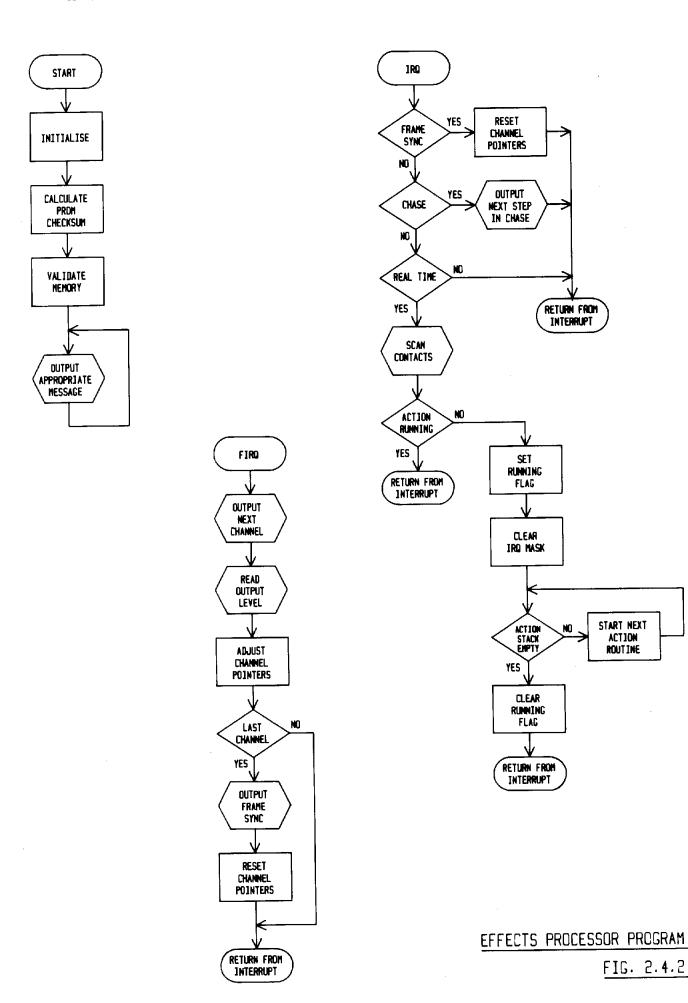

#### 2.4.2.5 Effects Processor Program

The Effects processor program consists mainly of interrupt and action routines. Interrupt requests are generated by the two PIAs in response to multiplex sync pulses, the M24 Frame Sync signal, the Chase pulse generator output and Real Time Interrupt signals. Action routines are initiated in response to panel button operations and are added to an Action Stack for processing between interrupts.

On power-up, the system is initialised and the PROM checksum and RAM validation routines carried out. The MPU then enters the background loop to output the appropriate message.

The interrupt routines are as follows:

### i) Multiplex Sync Pulses

In order to ensure that channel levels are output at the correct rate, these interrupts are generated via the Fast Interrupt Request (FIRQ) input of the MPU.

On receipt of a FIRQ, the MPU outputs the on/off states of the next channel and, if necessary, reads the current overall output for use in the LOAD OUTPUT action routine. The channel pointers are then adjusted and, if the channel is the last one in the frame (i.e. channel 60), the MPU outputs a Local Frame Sync signal and resets the channel pointers before returning to background or action level.

#### ii) Frame Sync Pulse

On receipt of a frame sync IRQ, the MPU carries out a routine to reset the channel pointers.

# iii) Chase IRQ

When an IRQ is received from the Chase pulse generator, a routine to output the next step in the chase is carried out.

#### iv) Real Time IRQ

On receipt of a Real Time IRQ, the MPU scans the contacts and displays and, if appropriate, adds any new routines to the Action Stack for processing at action level. If an action routine is in progress, the MPU then returns to action level. If not, the Action Running flag is set and the IRQ Mask cleared, prior to testing the Action Stack; if this is empty, the Action Running Flag is cleared and the MPU returns to background level, but if not the MPU jumps to the next routine on the stack.

Issue 1

#### CHAPTER 3

#### CONTROL PANEL BOARD (Ref.1833)

### Drawing No. 6A26904

#### 3.1 INTRODUCTION

This board is mounted immediately behind the M24 control panel and carries the panel push-buttons and displays, and the Master Faders and Fade Duration controls. The board connects to the Motherboard via a 20-way ribbon cable.

In addition to the panel controls and displays, the board carries a microprocessor (Panel MPU) and a 2Kbyte PROM. The MPU scans the button contacts and the displays and communicates with the Motherboard Processor via a serial link.

### 3.2 THE MICROPROCESSOR

The Panel MPU, IC11, is a Motorola MC6803 8-bit microcomputer. It incorporates an 8-bit parallel interface port, which is used to scan the push-buttons and the displays, and a serial communications interface, which provides the link with the Motherboard Processor. In addition, the MPU includes a programmable timer, which is not used, and 128 bytes of random access memory (RAM).

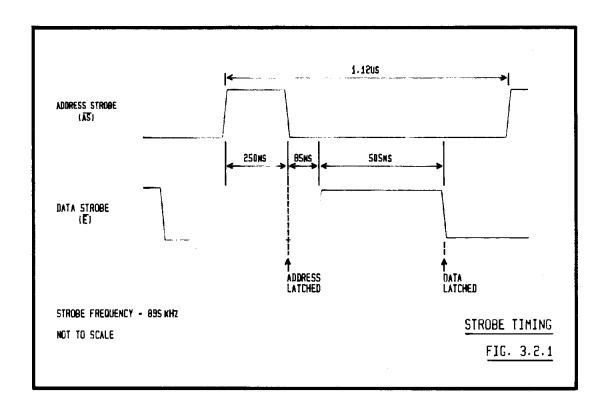

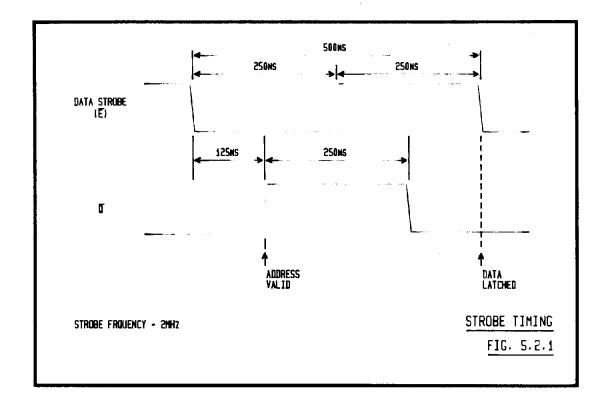

Communication with the PROM and the channel control wheel is is by means of an eight-bit address bus (A8 - A15) and a multiplexed Data/Address Bus (D0/A0 - D7/A7). An Address Strobe ('AS') pulse generated by the MPU permits the separation of the address signals (in latch ICl2), to produce address lines A0 - A7. This gives a total available address space (including those addresses internal to the microprocessor, i.e. RAM, etc.) of 64Kbytes (\$0000 - \$FFFF). Correct data timing is ensured by a Data Strobe pulse ('E').

The MPU derives the strobe signals from a 3.57945MHz crystal, XL, the output of which is divided by four to give a strobe frequency of 895kHz. The timing of the 'AS' and 'E' signals is shown in Fig. 3.2.1.

### 3.3 PANEL PROCESSOR ADDRESSES

Address lines Al3 - Al5 are decoded by IC7 to produce enable signals for the Program PROM (\$E000 - \$FFFF), External RAM (\$8000 - \$9FFF), Wheel Interface (\$4000 - \$5FFF) and Interrupt Latch (\$2000 - \$3FFF). Note that the addresses between \$0000 and \$00FF are assigned to locations within the MPU, the address bus being internally decoded.

# 3.3.1 Program PROM

The Program PROM, IC14, is a type 2716 2Kbyte EPROM located at addresses \$F800 to \$FFFF. The device is selected by a low output from pin 9 of decoder IC7 when Al3 - Al5 are all high, and its output is enabled by the low output of NAND gate IC8/12 when R/W and 'E' are both high.

It should be noted that the printed circuit board has been designed to allow an 8Kbyte PROM (type 2764) to be fitted and that the pin numbers shown on the circuit diagram apply to this device. The 2716 PROM is fitted with pin 1 in pin 3 of the dual-in-line socket.

### 3.3.2 External RAM

Provision is made for a type 6116LP-4 2Kbyte RAM (IC13) at addresses \$8000 - \$87FF. The device is selected by a low output from pin 5 of decoder IC7 and, for MPU read actions, its outputs are enabled by the output of NAND gate IC8/12 (see previous section). For write actions, a Write Enable pulse is produced by NAND gate IC8/6, which is enabled by 'E' and inverted R/W, except during Reset. IC13 is not normally fitted.

# 3.3.3 Wheel Interface

A fourteen pin DIL socket, SK1, is provided for connection to the channel control fader wheel. The movement of the wheel may be read via addresses \$4000 -\$5FFF (\$4000 is normally used). When this takes place, a strobe pulse (STB) is generated by gating 'E' with the inverted output from pin 3 of IC7 in NAND gate IC8/8.

### 3.3.4 Interrupt Latch

Monostable IC4/7 is used as a latch and its output is applied to the IRQl input (pin 5) of the MPU. The device is reset by a low output from pin 2 of IC7, generated when the MPU accesses any address in the range \$2000 - \$3FFF. Address \$2000 is normally used.

### 3.3.5 Address Locations within the MPU

The Panel MPU incorporates 128 bytes of RAM (addresses \$0000 - \$000FF), a Serial Communications Interface (\$0000 - \$00013), a programmable Timer (\$0004 - \$000F) and an 8-bit parallel interface port (\$0000 & \$0002). The Timer is not used in this application and its associated registers must not be accessed by the user.

### 3.4 SERIAL COMMUNICATIONS INTERFACE

Addresses \$0010 - \$0013 provide access to a Serial Communications Interface which is used to transfer data to and from the Motherboard Processor. The Transmit output appears on MPU pin 12 (Port 2, bit 4) and is routed via buffer IC3/6 to pin 2 of connector PL1, while the Receive input is routed via PL1 pin 3 and buffer IC3/4 to pin 11 (Port 2, bit 3) of the MPU. The transmission rate is determined by a clock signal (Tx/Rx CLK) which is generated on the Motherboard and routed via PL1 pin 1 and buffer IC3/2 to pin 10 (Port 2, bit 2) of the MPU.

The four Serial Communications Interface addresses provide access to the following registers:

| \$0010 | Rate and Mode Register (write only). |

|--------|--------------------------------------|

| \$0011 | Control and Status Register.         |

| \$0012 | Receive Data Register (read only).   |

| \$0013 | Transmit Data Register (write only). |

Note: The Serial Communications Interface port (Port 2) may also be used as a parallel interface and addresses \$0001 and \$0003 provide access to its associated Data and Data Direction registers. The Data Register (\$0003) is not used in this application, but the Data Direction Register (\$0001) is initialised so that lines 0 and 4 are outputs and lines 1 and 3 inputs.

#### 3.5 DISPLAY AND PUSH-BUTTON MATRICES

The 8-bit parallel interface port (Port 1) is used to control the panel displays and indicators and to detect button actions. Each time the equipment is switched on, the individual lines of the port are programmed by the MPU so that bits 0-6 will function as outputs and bit 7 as an input. This is done by means of a Data Direction Register located at address \$0000. The port itself is accessible to the MPU via a Data Register located at address \$0002.

# 3.5.1 Display Matrix

The displays and indicators are wired as an eight-by-eight matrix. The rows are connected to a shift register, ICl, which receives data from Port 1, bit 6 and clock pulses from Port 1, bit 1. The outputs of ICl are applied to darlington drivers (IC2/10 - IC2/16 and VT11) each of which provides the common return for one of the rows.

The columns of the display matrix are driven by PNP darlington transistors VT3 - VT10, which are themselves controlled by the outputs of decoder IC5. The select inputs to the latter are from bits 3-5 of MPU Port 1 and the device is enabled by the output (DISP EN) of monostable IC4/9.

### 3.5.2 Button Matrix

The panel push-buttons are wired as an eight-by-five matrix. The rows are selected by the outputs of decoder IC9, the binary inputs to which are provided by a counter (IC10), clocked by the same signal (MPU Port 1, bit 1) as shift register IC1.

The columns are scanned by means of data selector IC6, the select inputs to which are bits 3-5 from Port 1 of the MPU. The state of the selected button matrix column appears on pin 3 of IC6 and is applied to bit 7 of MPU Port 1. Each contact has an associated diode to prevent interaction between the rows and columns which could lead to false results when several buttons are operated at once.

Because the select inputs to IC6 are the same signals as are used to select the required column in the display matrix, selection of a column in the latter results in the simultaneous selection of the corresponding column in the button matrix. This makes it possible for the MPU to scan both matrices at the same time.

### 3.5.3 Display and Contact Scan

On completion of each display and contact scan, monostable IC4/9 is triggered by a positive-going output from Port 1, bit 2. The resulting 1.5ms pulse (DISP EN) enables the display drivers and, on its trailing edge, triggers monostable IC4/7. The inverted output (pin 7) of the latter device is applied to pin 5 (IRQ1) of the MPU, generating an interrupt request.

The output of IC4/7 is also fed back via R29 to timing capacitor C9. Once the device is triggered C9 cannot charge because of the low pin 7 output and the monostable will therefore never time-out. It thus functions as a flip-flop set by the back edge of DISP EN and reset (on pin 3) by a low output from pin 2 of IC7 (see section 3.3.4).

When the MPU responds to the interrupt request, it first writes to address \$2000 to reset IC4/7 and then enters a routine to read one column of the button matrix and set-up the corresponding column of the display.

At the start of the scan, the required column in the two matrices is selected by means of MPU Port 1, bits 3-5 and counter ICl0 is reset by a high output on bit 0. At the same time, data for the first row of the display matrix is output on bit 6.

Bit Ø of Port 1 is then set low, allowing IC1Ø to count, and bit 1 is set high. The latter acts as a clock pulse to IC1Ø, thus selecting the first row of the button matrix, and also shifts the data on bit 6 into shift register IC1. The state of the selected contact is now read via bit 7 and, when this has been done and the information stored in the RAM, bit 1 is set low, ready for the next clock pulse. The data for the next row of the display matrix is then output on bit 6 and the process is repeated until all eight rows have been scanned.

On completion of the above, shift register ICl will contain the on/off states for all the display segments and indicators in the selected column of the display matrix. The MPU now sets bit 2 of

Port 1 high and this triggers monostable IC4/9. The latter device produces a 1.5ms DISP EN pulse which enables decoder IC5, thus switching on the transistor (VT3 - VT10) which drives the selected display column.

When IC4/9 has been triggered, the MPU returns to its normal processing, but at the end of the DISP EN pulse, it is again interrupted and the next column is scanned. The sequence repeats continually for each column in turn, so that each button contact is scanned about every 12ms and each display column is enabled for 1.5ms of this time. The frequency of this is such that the displays appear to be constantly illuminated.

### 3.6 MASTER FADERS AND FADE DURATION CONTROLS

The Master Faders and Fade Duration controls are mounted on the Control Panel Board, but are connected directly to the Motherboard via connector PLL.

# 3.7 RESET CIRCUIT

The reset circuit is formed by transistors VTl and VT2, and their associated components. The circuit has two functions: firstly, to generate a reset pulse each time the equipment is switched on, thus ensuring that the MPU enters its start-up procedure correctly, and secondly, to inhibit processor operation if the voltage on the +5V rail varies by more than the allowed tolerance.

As the +5V rail (routed from the Motherboard via connector PL1) becomes established at switch on, VT2 will initially switch on because of the potential divider action of R7, R2, R3 and R11. This pulls the Reset line low. When the rail reaches +3.9V, zener diode D2 conducts and the voltage on the base of VT1 starts to rise until, with about +4.5V on the rail, this transistor switches on. VT2 is thus switched off and C1 begins to charge via R4. The Reset line will therefore rise with a time constant C1/R4.

If the +5V rail falls below +4.5V, VTl turns off. This turns on VT2, clamping the Reset line to ØV. Also, the MPU may be reset by means of a manual reset switch, SWl.

In order to ensure correct MPU operation, three of the Port 2 lines must be held in the correct states during Reset. In addition to the RST pin (MPU pin 6) therefore, the Reset signal is connected via diodes to bits 0 and 2 of Port 2 (pins 8 and 10) and bit 1 (pin 9) is connected via a resistor to +5V.

The Reset signal is also applied to NAND gate IC8/6, to prevent write pulses to the External RAM, and to monostable IC4/9, to inhibit the displays and indicators.

#### CHAPTER 4

### WHEEL INTERFACE BOARD (Ref. 1706)

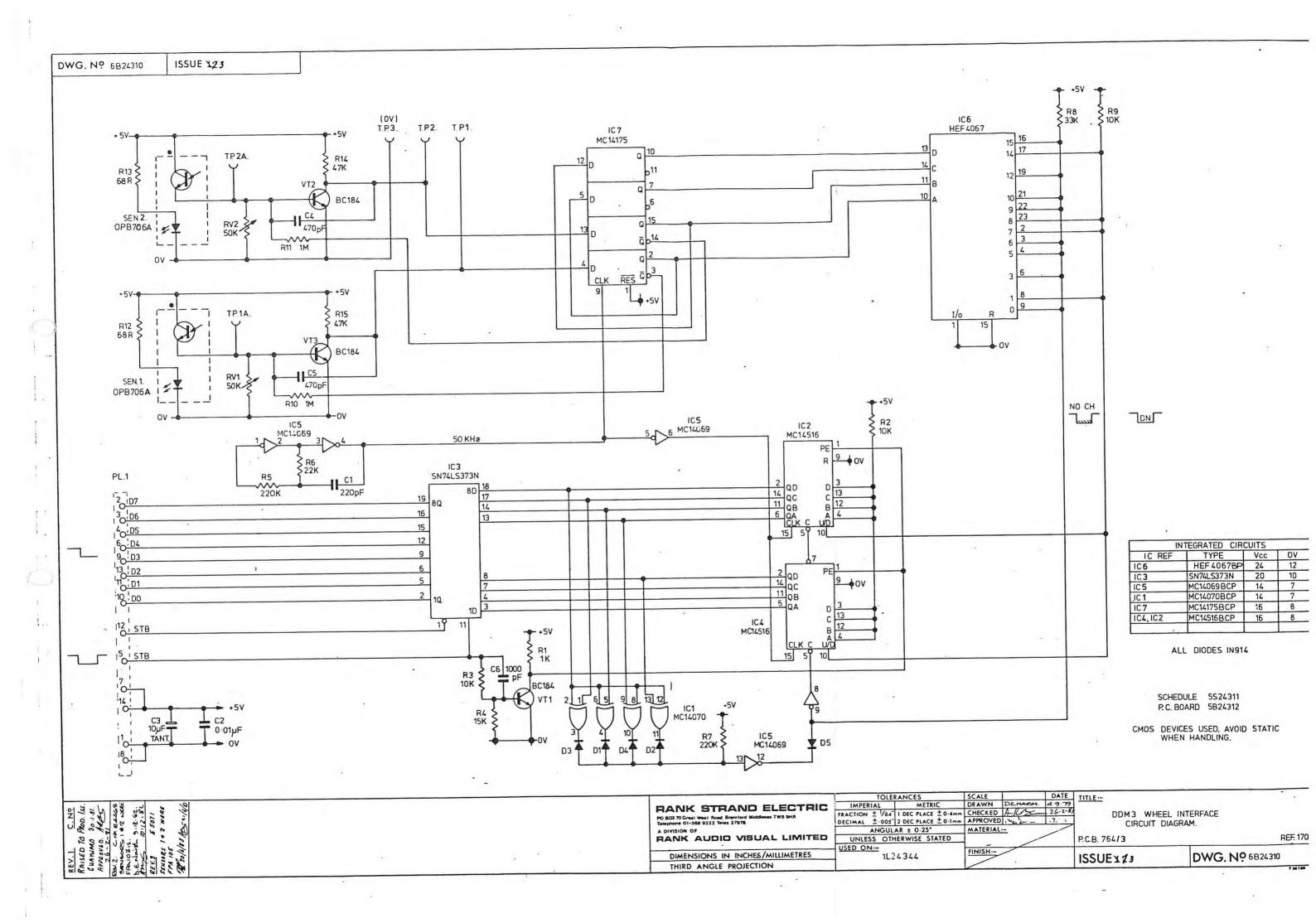

#### Drawing No. 6B24310

### 4.1 INTRODUCTION

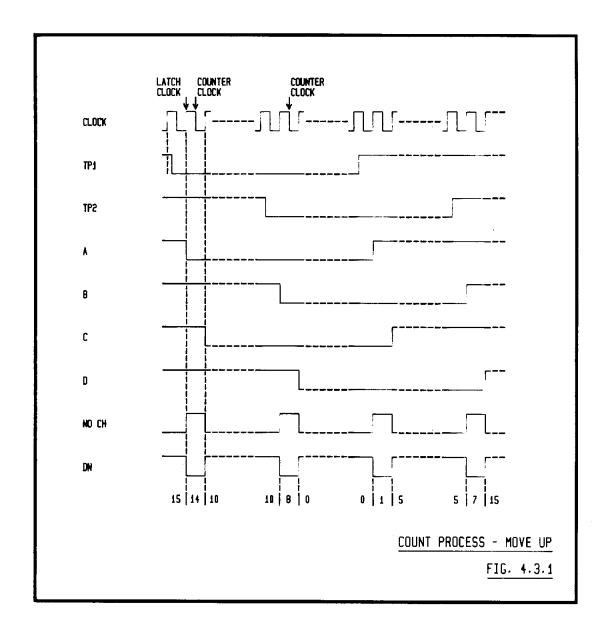

This board converts the movement of the fader wheel into a form which can be read by a microprocessor. The wheel incorporates an inner disc with 212 slots which move past two photo-sensor devices as the wheel is operated. The extent of the movement is determined by counting the number of slots which pass the sensors and the direction by the phase relationship of the signals from the two sensors. This information appears on the outputs of an eight-bit latch in response to a strobe signal generated by the microprocessor. When the latch contents are read, the count is reset to zero, so that the output always represents the change in wheel position since the last read action.

### 4.2 MOVEMENT DETECTOR

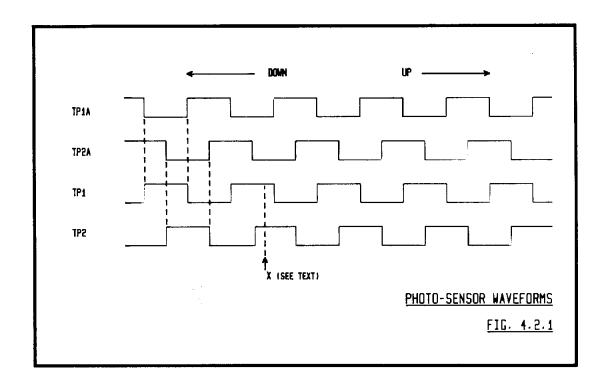

The two photo-sensor devices, SEN1 and SEN2, each consist of an LED and a photo-transistor. Light generated by each LED is reflected from the surface of the disc and detected by the corresponding photo-transistor. The sensors and positioned so that the signals which they produce are  $90^{\circ}$  out of phase with each other as shown in Fig. 4.2.1.

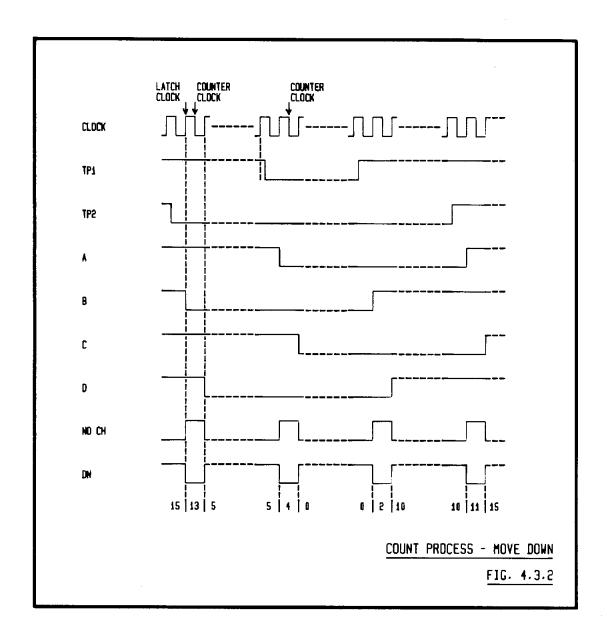

The outputs from SEN1 and SEN2 are amplified by VT3 and VT2 respectively, and applied to input pins 4 and 13 of four-bit latch IC7. The latch is clocked by a 50kHz signal generated by an oscillator formed by IC5/2 and IC5/4, and their associated components.