# processor handbook

digital equipment corporation

#### **DEC Typesetting**

This Handbook was typed and edited with the aid of the DECsystem 10 timesharing system and type was set via a DEC computer typesetting system.

Copyright 1971 by Digital Equipment Corporation

PDP, DEC, UNIBUS are registerd trademarks of Digital Equipment Corporation

The material in this handbook is for information purposes only and is subject to change without notice

The PDP-11 is a family of upward-compatible computer systems. We believe that these systems represent a significant departure from traditional methods of computer design.

The initial design step was the development of a totally new language, notation, and theory of computers called the Instruction Set Processor (ISP). This language provides a concise and powerful generalized method for defining an arbitrary computer system and its operation. Along with the development of ISP, a PDP-10 program was written for simulating the operation of any computer system on the basis of its ISP description. With the aid of ISP and the machine simulation program, benchmark comparison tests were run on a large number of potential computer designs. In this manner it was possible to evaluate a variety of design choices and compare their features and advantages, without the time and expense of actually constructing physical prototypes.

Since the main design objective of the PDP-11 was to optimize total system performance, the interaction of software and hardware was carefully considered at every step in the design process. System programmers continually evaluated the efficiency of the code which would be produced by the system software, the ease of coding a program, the speed of real-time response, the power and speed that could be built into a system executive, the ease of system resource management, and numerous other potential software considerations.

The current PDP-11 Family is the result of this design effort. We believe that its general purpose register and UNIBUS organization provides unparalleled power and flexibility. This design is the basis for our continuing commitment to further PDP-11 product development.

Thus the PDP-11 Family is at once a new concept in computer systems, and a tested and tried system. The ultimate proof of this new design approach has come from the large and rapidly increasing number of PDP-11 users all around the world.

Kenneth H. Olsen President, Digital Equipment Corporation

# Introduction

This Handbook provides basic information about the PDP-11/20 general purpose 16-bit computer, the PDP-11/15 OEM computer, and the PDP-11R20 rugged computer. Since these computers are functionally identical, all statements about the PDP-11/20 apply also to the PDP-11/15 and the PDP-11R20. Part I describes the processor, its major components and how the PDP-11/20 is programmed. Part II is a summary of PDP-11 software; and Part III describes PDP-11 time-sharing, communications, and data acquisition and control systems.

The PDP-11/20 Processor Handbook is supplemented by the PDP-11 Peripherals and Interfacing Handbook, which includes detailed descriptions of PDP-11 peripherals, options, and the UNIBUS (the single data bus common to all PDP-11 family computers).

Manuals covering the various PDP-11 software packages (Paper Tape, Disk Operating System, FORTRAN, etc.) and detailed hardware maintenance manuals are also available.

# TABLE OF CONTENTS

# PART I PDP-11/20 PDP-11/15 PDP-11R20

| CHAPTER 1 INTRODUCTION                                                                                                                                                                                             | 1                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 1.1 PDP-11 FAMILY<br>1.2 GENERAL CHARACTERISTICS<br>1.3 PERIPHERALS/OPTIONS<br>1.4 SOFTWARE<br>1.5 DATA COMMUNICATIONS<br>1.6 DATA ACQUISITION AND CONTROL                                                         | 1<br>6<br>7<br>8 |

| CHAPTER 2 SYSTEM ARCHITECTURE                                                                                                                                                                                      | 9                |

| 2.1 UNIBUS<br>2.2 CENTRAL PROCESSOR<br>2.3 CORE MEMORY<br>2.4 SYSTEM INTERACTION<br>2.5 AUTOMATIC PRIORITY INTERRUPTS                                                                                              | 10<br>13<br>15   |

| CHAPTER 3 ADDRESSING MODES                                                                                                                                                                                         | 19               |

| 3.1 SINGLE OPERAND ADDRESSING<br>3.2 DOUBLE OPERAND ADDRESSING<br>3.3 DIRECT ADDRESSING<br>3.4 DEFERRED (INDIRECT) ADDRESSING<br>3.5 USE OF PC AS GENERAL REGISTER<br>3.6 USE OF STACK POINTER AS GENERAL REGISTER | 22<br>28         |

| CHAPTER 4 INSTRUCTION SET                                                                                                                                                                                          | 37               |

| <ul> <li>4.1 INTRODUCTION</li></ul>                                                                                                                                                                                |                  |

| CHAPTER 5 PROGRAMMING TECHNIQUES       | 108 |

|----------------------------------------|-----|

| 5.1 STACK                              | 108 |

| 5.2 SUBROUTINE LINKAGE                 |     |

| 5.3 INTERRUPTS                         |     |

| 5.4 REENTRANCY                         |     |

| 5.5 POSITION INDEPENDENT CODE          |     |

| 5.6 RECURSION                          |     |

| 5.7 CO-ROUTINES                        | 124 |

|                                        |     |

| CHAPTER 6 SPECIFICATIONS               |     |

|                                        |     |

| 6.1 PDP-11/20 AND PDP-11/15 COMPUTER   |     |

| 6.2 PDP-11R20 RUGGEDIZED COMPUTER      |     |

| 6.3 INSTALLATION PROCEDURE             |     |

| 6.4 SYSTEM UNITS AND CABLES            |     |

| 6.5 POWER SUPPLY                       |     |

| 6.6 TELETYPE REQUIREMENTS              |     |

|                                        |     |

| CHAPTER 7 CONSOLE OPERATION            |     |

| CHAPTER 8 EXTENDED ARITHMETIC ELEMENT  | 149 |

| CHAFTER O EXTENDED ARTTHINETIC ELEMENT | 143 |

| 8.1 DESCRIPTION                        | 143 |

| 8.2 PROGRAMMING                        |     |

| 8.3 INSTRUCTIONS                       |     |

| 8.4 PROGRAMMING EXAMPLES               |     |

|                                        |     |

# PART II SOFTWARE

| CHAPTER 1 PAPER TAPE SOFTWARE       155         1.1 PAL-11 ASSEMBLER       155         1.2 EDITING SOURCE PROGRAM       156         1.3 LOADERS AND DUMPS       156         1.4 FLOATING POINT PACKAGE       157         1.5 ON-LINE DEBUGGING       159         1.6 INPUT /OUTPUT EXECUTIVE       159         1.7 BASIC LANGUAGE       160         CHAPTER 2 DISK OPERATING SYSTEM       163         2.1 DESCRIPTION       163         2.2 ASSEMBLY LANGUAGE       165         2.3 TEXT EDITOR       166         2.4 ON-LINE DEBUGGING       166         2.5 FILE UTILITY PACKAGE       166         2.6 LINKER       166         2.7 LIBRARIAN       168         CHAPTER 3 FORTRAN IV       169         CHAPTER 4 COMMUNICATIONS SOFTWARE (COMTEX-11)       171         4.1 APPLICATIONS       171         4.2 DESCRIPTION       171         4.3 DISTRIBUTION       172         4.4 CORE REQUIREMENTS       173         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)       175         5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-RPOGRAMMING       176 <th>INTRODUCTION</th> <th>153</th> | INTRODUCTION                                  | 153 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----|

| 1.2 EDITING SOURCE PROGRAM.       156         1.3 LOADERS AND DUMPS       156         1.4 FLOATING POINT PACKAGE       157         1.5 ON-LINE DEBUGGING       159         1.6 INPUT /OUTPUT EXECUTIVE       159         1.7 BASIC LANGUAGE       160         CHAPTER 2 DISK OPERATING SYSTEM         163       2.1 DESCRIPTION         2.1 DESCRIPTION       163         2.2 ASSEMBLY LANGUAGE       165         2.3 TEXT EDITOR       166         2.4 ON-LINE DEBUGGING       166         2.5 FILE UTILITY PACKAGE       166         2.6 LINKER       166         2.7 LIBRARIAN       168         CHAPTER 4 COMMUNICATIONS SOFTWARE (COMTEX-11)         4.1 APPLICATIONS       171         4.2 DESCRIPTION       171         4.3 DISTRIBUTION       172         4.4 CORE REQUIREMENTS       173         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)         175       5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING       176         5.4 MULTI-PROGRAMMING       176         5.6 OPERATOR COMMUNICATION       177     <                                                        |                                               |     |

| 1.2 EDITING SOURCE PROGRAM.       156         1.3 LOADERS AND DUMPS       156         1.4 FLOATING POINT PACKAGE       157         1.5 ON-LINE DEBUGGING       159         1.6 INPUT /OUTPUT EXECUTIVE       159         1.7 BASIC LANGUAGE       160         CHAPTER 2 DISK OPERATING SYSTEM         163       2.1 DESCRIPTION         2.1 DESCRIPTION       163         2.2 ASSEMBLY LANGUAGE       165         2.3 TEXT EDITOR       166         2.4 ON-LINE DEBUGGING       166         2.5 FILE UTILITY PACKAGE       166         2.6 LINKER       166         2.7 LIBRARIAN       168         CHAPTER 4 COMMUNICATIONS SOFTWARE (COMTEX-11)         4.1 APPLICATIONS       171         4.2 DESCRIPTION       171         4.3 DISTRIBUTION       172         4.4 CORE REQUIREMENTS       173         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)         175       5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING       176         5.4 MULTI-PROGRAMMING       176         5.6 OPERATOR COMMUNICATION       177     <                                                        | 1.1 PAL-11 ASSEMBLER                          | 155 |

| 1.3 LOADERS AND DUMPS       156         1.4 FLOATING POINT PACKAGE       157         1.5 ON-LINE DEBUGGING       159         1.6 INPUT /OUTPUT EXECUTIVE       159         1.7 BASIC LANGUAGE       160         CHAPTER 2 DISK OPERATING SYSTEM       163         2.1 DESCRIPTION       163         2.2 ASSEMBLY LANGUAGE       165         2.3 TEXT EDITOR       166         2.4 ON-LINE DEBUGGING       166         2.5 FILE UTILITY PACKAGE       166         2.6 LINKER       167         2.7 LIBRARIAN       168         CHAPTER 3 FORTRAN IV       169         CHAPTER 4 COMMUNICATIONS SOFTWARE (COMTEX-11)       171         4.1 APPLICATIONS       171         4.2 DESCRIPTION       172         4.4 CORE REQUIREMENTS       173         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)       175         5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING       176         5.5 INPUT / OUTPUT       176         5.6 OPERATOR COMMUNICATION       177                                                                                                                         | 1.2 EDITING SOURCE PROGRAM                    | 156 |

| 1.4 FLOATING POINT PACKAGE       157         1.5 ON-LINE DEBUGGING       159         1.6 INPUT/OUTPUT EXECUTIVE       159         1.7 BASIC LANGUAGE       160         CHAPTER 2 DISK OPERATING SYSTEM         163       2.1 DESCRIPTION         163       2.2 ASSEMBLY LANGUAGE         165       2.3 TEXT EDITOR         166       2.4 ON-LINE DEBUGGING         166       2.4 ON-LINE DEBUGGING         166       2.4 ON-LINE DEBUGGING         2.5 FILE UTILITY PACKAGE       166         2.6 LINKER       167         2.7 LIBRARIAN       168         CHAPTER 3 FORTRAN IV         169       CHAPTER 4 COMMUNICATIONS SOFTWARE (COMTEX-11)         171       4.2 DESCRIPTION         171       4.2 DESCRIPTION         172       4.4 CORE REQUIREMENTS         173       CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)         175       5.1 LANGUAGES SUPPORTED         5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.4 MULTI-PROGRAMMING       176         5.4 MULTI-PROGRAMMING       176         5.4 MULTI-PROGRAMMING       176         5.6 OPERATOR COMMUNICATION       177    <                                                     |                                               |     |

| 1.5 ON-LINE DEBUGGING       159         1.6 INPUT / OUTPUT EXECUTIVE       159         1.7 BASIC LANGUAGE       160         CHAPTER 2 DISK OPERATING SYSTEM         163       2.1 DESCRIPTION         2.1 DESCRIPTION       163         2.2 ASSEMBLY LANGUAGE       165         2.3 TEXT EDITOR       166         2.4 ON-LINE DEBUGGING       166         2.5 FILE UTILITY PACKAGE       166         2.6 LINKER       167         2.7 LIBRARIAN       168         CHAPTER 3 FORTRAN IV         169       164         CHAPTER 4 COMMUNICATIONS SOFTWARE (COMTEX-11)         171       4.1 APPLICATIONS         171       4.2 DESCRIPTION         171       4.3 DISTRIBUTION         172       4.4 CORE REQUIREMENTS         173       174         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)       175         5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING       176         5.4 MULTI-PROGRAMMING       176         5.6 OPERATOR COMMUNICATION       177                                                                                                                       | 1.4 FLOATING POINT PACKAGE                    | 157 |

| 1.6 INPUT/OUTPUT EXECUTIVE       159         1.7 BASIC LANGUAGE       160         CHAPTER 2 DISK OPERATING SYSTEM         163       2.1 DESCRIPTION         2.1 DESCRIPTION       163         2.2 ASSEMBLY LANGUAGE       163         2.3 TEXT EDITOR       166         2.4 ON-LINE DEBUGGING       166         2.5 FILE UTILITY PACKAGE       166         2.6 LINKER       167         2.7 LIBRARIAN       168         CHAPTER 3 FORTRAN IV         169       CHAPTER 4 COMMUNICATIONS SOFTWARE (COMTEX-11)         171       4.1 APPLICATIONS         4.1 APPLICATIONS       171         4.2 DESCRIPTION       171         4.3 DISTRIBUTION       172         4.4 CORE REQUIREMENTS       173         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)         175       5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176       176         5.3 MEMORY EFFICIENCY       176       176         5.4 MULTI-PROGRAMMING       176       176         5.6 OPERATOR COMMUNICATION       176       176                                                                                                                                                                | 1.5 ON-LINE DEBUGGING                         | 159 |

| CHAPTER 2 DISK OPERATING SYSTEM       163         2.1 DESCRIPTION       163         2.2 ASSEMBLY LANGUAGE       165         2.3 TEXT EDITOR       166         2.4 ON-LINE DEBUGGING       166         2.5 FILE UTILITY PACKAGE       166         2.6 LINKER       166         2.7 LIBRARIAN       168         CHAPTER 3 FORTRAN IV       169         CHAPTER 4 COMMUNICATIONS SOFTWARE (COMTEX-11)       171         4.1 APPLICATIONS       171         4.2 DESCRIPTION       171         4.3 DISTRIBUTION       172         4.4 CORE REQUIREMENTS       173         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)       175         5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING       176         5.5 INPUT/OUTPUT       176         5.6 OPERATOR COMMUNICATION       177                                                                                                                                                                                                                                                                                                        | 1.6 INPUT/OUTPUT EXECUTIVE                    | 159 |

| 2.1 DESCRIPTION       163         2.2 ASSEMBLY LANGUAGE       165         2.3 TEXT EDITOR       166         2.4 ON-LINE DEBUGGING       166         2.5 FILE UTILITY PACKAGE       166         2.6 LINKER       166         2.7 LIBRARIAN       168         CHAPTER 3 FORTRAN IV       169         CHAPTER 4 COMMUNICATIONS SOFTWARE (COMTEX-11)       171         4.1 APPLICATIONS       171         4.2 DESCRIPTION       171         4.3 DISTRIBUTION       172         4.4 CORE REQUIREMENTS       173         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)       175         5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING       176         5.5 INPUT / OUTPUT       176         5.6 OPERATOR COMMUNICATION       177                                                                                                                                                                                                                                                                                                                                                        | 1.7 BASIC LANGUAGE                            | 160 |

| 2.1 DESCRIPTION       163         2.2 ASSEMBLY LANGUAGE       165         2.3 TEXT EDITOR       166         2.4 ON-LINE DEBUGGING       166         2.5 FILE UTILITY PACKAGE       166         2.6 LINKER       167         2.7 LIBRARIAN       168         CHAPTER 3 FORTRAN IV       169         CHAPTER 4 COMMUNICATIONS SOFTWARE (COMTEX-11)       171         4.1 APPLICATIONS       171         4.2 DESCRIPTION       171         4.3 DISTRIBUTION       172         4.4 CORE REQUIREMENTS       173         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)       175         5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING       176         5.5 INPUT / OUTPUT       176         5.6 OPERATOR COMMUNICATION       177                                                                                                                                                                                                                                                                                                                                                        | CHAPTER 2 DISK OPERATING SYSTEM               | 163 |

| 2.2 ASSEMBLY LANGUAGE       165         2.3 TEXT EDITOR       166         2.4 ON-LINE DEBUGGING       166         2.5 FILE UTILITY PACKAGE       166         2.6 LINKER       167         2.7 LIBRARIAN       168         CHAPTER 3 FORTRAN IV       169         CHAPTER 4 COMMUNICATIONS SOFTWARE (COMTEX-11)       171         4.1 APPLICATIONS       171         4.2 DESCRIPTION       171         4.3 DISTRIBUTION       172         4.4 CORE REQUIREMENTS       173         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)       175         5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING       176         5.5 INPUT / OUTPUT       176         5.6 OPERATOR COMMUNICATION       177                                                                                                                                                                                                                                                                                                                                                                                          |                                               | 11  |

| 2.3 TEXT EDITOR       166         2.4 ON-LINE DEBUGGING       166         2.5 FILE UTILITY PACKAGE       166         2.6 LINKER       167         2.7 LIBRARIAN       168         CHAPTER 3 FORTRAN IV         169         CHAPTER 4 COMMUNICATIONS SOFTWARE (COMTEX-11)         4.1 APPLICATIONS       171         4.2 DESCRIPTION       171         4.3 DISTRIBUTION       172         4.4 CORE REQUIREMENTS       173         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)         175         5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING       176         5.5 INPUT / OUTPUT       176         5.6 OPERATOR COMMUNICATION       177                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                               |     |

| 2.4 ON-LINE DEBUGGING       166         2.5 FILE UTILITY PACKAGE       166         2.6 LINKER       167         2.7 LIBRARIAN       168         CHAPTER 3 FORTRAN IV         169         CHAPTER 4 COMMUNICATIONS SOFTWARE (COMTEX-11)         4.1 APPLICATIONS       171         4.2 DESCRIPTION       171         4.3 DISTRIBUTION       172         4.4 CORE REQUIREMENTS       173         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)         175         5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING       176         5.5 INPUT / OUTPUT       176         5.6 OPERATOR COMMUNICATION       177                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |     |

| 2.5 FILE UTILITY PACKAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |     |

| 2.6 LINKER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.4 ON-LINE DEBUGGING                         | 166 |

| 2.7 LIBRARIAN       168         CHAPTER 3 FORTRAN IV       169         CHAPTER 4 COMMUNICATIONS SOFTWARE (COMTEX-11)       171         4.1 APPLICATIONS       171         4.2 DESCRIPTION       171         4.3 DISTRIBUTION       172         4.4 CORE REQUIREMENTS       173         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)       175         5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING.       176         5.5 INPUT / OUTPUT       176         5.6 OPERATOR COMMUNICATION.       177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                               |     |

| CHAPTER 3 FORTRAN IV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |     |

| CHAPTER 4 COMMUNICATIONS SOFTWARE (COMTEX-11)       171         4.1 APPLICATIONS       171         4.2 DESCRIPTION       171         4.3 DISTRIBUTION       172         4.4 CORE REQUIREMENTS       173         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)         175       5.1 LANGUAGES SUPPORTED         5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING       176         5.5 INPUT / OUTPUT       176         5.6 OPERATOR COMMUNICATION       177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.7 LIBRARIAN                                 | 168 |

| 4.1 APPLICATIONS.       171         4.2 DESCRIPTION       171         4.3 DISTRIBUTION       172         4.4 CORE REQUIREMENTS       173         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)         175         5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING.       176         5.5 INPUT / OUTPUT       176         5.6 OPERATOR COMMUNICATION.       177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CHAPTER 3 FORTRAN IV                          | 169 |

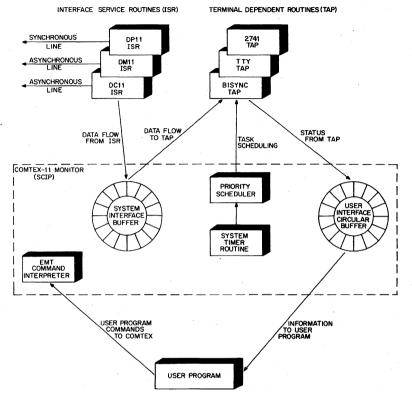

| 4.2 DESCRIPTION       171         4.3 DISTRIBUTION       172         4.4 CORE REQUIREMENTS       173         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)         5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING       176         5.5 INPUT / OUTPUT       176         5.6 OPERATOR COMMUNICATION       177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CHAPTER 4 COMMUNICATIONS SOFTWARE (COMTEX-11) | 171 |

| 4.2 DESCRIPTION       171         4.3 DISTRIBUTION       172         4.4 CORE REQUIREMENTS       173         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)         5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING       176         5.5 INPUT / OUTPUT       176         5.6 OPERATOR COMMUNICATION       177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                               |     |

| 4.3 DISTRIBUTION       172         4.4 CORE REQUIREMENTS       173         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)         175       5.1 LANGUAGES SUPPORTED         5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING.       176         5.5 INPUT/OUTPUT       176         5.6 OPERATOR COMMUNICATION       177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               |     |

| 4.4 CORE REQUIREMENTS       173         CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)         5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING.       176         5.5 INPUT/OUTPUT       176         5.6 OPERATOR COMMUNICATION       177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                               |     |

| CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)       175         5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING.       176         5.5 INPUT/OUTPUT       176         5.6 OPERATOR COMMUNICATION.       177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                               |     |

| 5.1 LANGUAGES SUPPORTED       175         5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING       176         5.5 INPUT/OUTPUT       176         5.6 OPERATOR COMMUNICATION       177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4.4 CORE REQUIREMENTS                         | 1/3 |

| 5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING       176         5.5 INPUT/OUTPUT       176         5.6 OPERATOR COMMUNICATION       177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CHAPTER 5 REAL TIME EXECUTIVE (RSX-11C)       | 175 |

| 5.2 SCHEDULING       176         5.3 MEMORY EFFICIENCY       176         5.4 MULTI-PROGRAMMING       176         5.5 INPUT/OUTPUT       176         5.6 OPERATOR COMMUNICATION       177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                               | 175 |

| 5.3 MEMORY EFFICIENCY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                               |     |

| 5.4 MULTI-PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                               | 1/6 |

| 5.5 INPUT/OUTPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                               | 1/6 |

| 5.6 OPERATOR COMMUNICATION177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                               |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |     |

# PART III SYSTEMS

| CHAPTER 1 TIMESHARING SYSTEM (RSTS-11)            |     |

|---------------------------------------------------|-----|

| 1.1 PROGRAMMING LANGUAGE                          | 181 |

| 1.2 PROGRAM DEVELOPMENT                           | 183 |

| 1.3 INPUT/OUTPUT                                  | 184 |

| 1.4 INTERNAL SYSTEM                               | 185 |

| 1.5 MONITOR FUNCTIONS                             | 185 |

| 1.6 SYSTEM ACCESS                                 |     |

|                                                   |     |

| CHAPTER 2 COMMUNICATIONS                          |     |

| 2.1 PDP-11 ARCHITECTURE                           | 187 |

| 2.2 HARDWARE                                      |     |

| 2.3 SOFTWARE                                      | 189 |

| 2.4 APPLICATIONS                                  |     |

|                                                   |     |

| CHAPTER 3 INDUSTRIAL DATA ACQUISITION AND CONTROL |     |

| 3.1 PROCESS INTERFACES                            |     |

| 3.2 REAL TIME OPERATING SYSTEM                    | 193 |

| 3.3 APPLICATIONS                                  |     |

|                                                   |     |

# APPENDIXES

| APPENDIX A INSTRUCTION REPERTOIRE    | <br>195 |

|--------------------------------------|---------|

| APPENDIX B MEMORY MAP                | <br>    |

| APPENDIX C INSTRUCTION SET PROCESSOR | <br>207 |

| INDEX |      |      | 221 |

|-------|------|------|-----|

|       | <br> | <br> |     |

PDP-11/20 PDP-11/15 PDP-11R20

# PART I CHAPTER 1

# INTRODUCTION

The PDP-11/20 is a powerful 16-bit computer in the medium-sized branch of the PDP-11 Family of computers. As the first member of the PDP-11 family it is the computer on which the whole family is based. It is a balanced, modular system with a wide range of features, peripherals, software and growth potential not normally found in 16-bit computers.

#### 1.1 THE PDP-11 FAMILY

The PDP-11 Family includes several processors, a large number of peripheral devices and options, and extensive software. PDP-11 machines are architecturally similar and hardware and software upwards compatible, although each machine has some of its own characteristics. New PDP-11 systems will be compatible with existing family members. The user can chose the system which is most suitable to his application, but as needs change or grow, he can easily add or change hardware. The major characteristics of PDP-11 family computers are listed in Table 1.

#### **1.2 GENERAL CHARACTERISTICS**

#### 1.2.1 The UNIBUS

All computer system components and peripherals connect to and communicate with each other on a single high-speed bus known as the UNIBUS -- the key to the PDP-11's many strengths. Since all system elements, including the central processor, communicate with each other in identical fashion via the UNIBUS, the processor has the same easy access to peripherals as it has to memory.

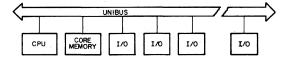

PDP 11 System Simplified Block Diagram

With bidirectional and asynchronous communications on the UNIBUS, devices can send, receive, and exchange data independently without processor intervention. For example, a cathode ray tube (CRT) display can refresh itself from a disk file while the central processor unit (CPU) attends to other tasks. Because it is asynchronous, the UNIBUS is compatible with devices operating over a wide range of speeds.

Device communications on the UNIBUS are interlocked. For each command issued by a "master" device, a response signal is received from a "slave" completing the data transfer. Device-to-device communication is completely independent of physical bus length and the response times of master and slave devices.

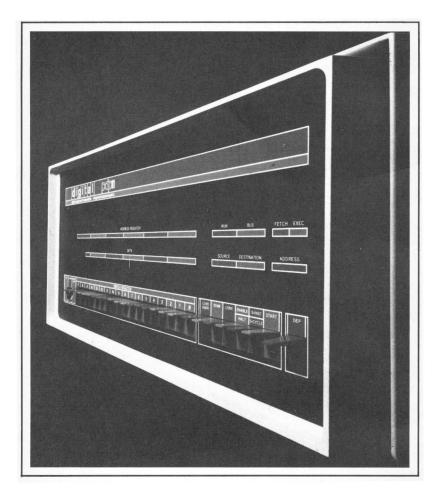

#### TABLE 1-1 PDP-11 Family Computers

PDP-11/20 PDP-11/45 PDP-11/05 PDP-11/15 PDP-11/R20 **KB11** CENTRAL PROCESSOR KD11-B KC11 **KA11** 16 **General Purpose Registers** 8 8 8 Instructions Basic Set Basic Set **Basic Set** Basic Set and MUL.DIV XOR.ASH.ASHC. MARK,SXT,SOB. SPL.RTT.MFPI. MTPD.MFPD.MTPI Yes Segmentation Option No No No Yes Hardware Stacks Yes Yes Yes Stack Overflow Yes Yes, fixed Yes, fixed Yes, fixed programmable Detection Automatic Priority single-line Single line four-line four-line interrupt multi-level multi-level multi-level multi-level PLUS (four line optional) 8 software levels Overlapped instruction No No No Yes Internal to Floating Point CPU(optional) Hardware No No No<sup>-</sup> Extended Arithmetic standard option option option Power Fail and standard option standard standard Auto-Restart Maximum 32K 32K 32K 128K Addressable (128K optional) **Memory Locations**

Interfaces to the UNIBUS are not time-dependent; there are no pulse-width or rise-time restrictions to worry about. The maximum transfer rate on the UNIBUS is one 16-bit word every 400 nanoseconds, or 2,500,000 words per second.

Input/output devices transferring directly to or from memory are given highest priority and may request bus mastership and steal bus and memory cycles during instruction operations. The processor resumes operation immediately after the memory transfer. Multiple devices can operate simultaneously at maximum direct memory access (DMA) rates by "stealing" bus cycles. The UNIBUS is further explained in Paragraph 2.2, Chapter 2; and is covered in considerable detail in Part II of the PDP-11 Peripherals and Interfacing Handbook.

#### 1.2.2 Central Processor

The central processor, connected to the UNIBUS as a subsystem, controls the time allocation of the UNIBUS for peripherals and performs arithmetic and logic operations and instruction decoding. It contains multiple high-speed general-purpose registers which can be used as accumulators, pointers, index registers, or as autoindexing pointers in autoincrement or autodecrement modes. The processor can perform data transfers directly between I/O devices and memory without disturbing the registers; does both single and double-operand addressing; handles both 16-bit word and 8-bit byte data; and, by using its dynamic stacking technique, allows nested interrupts and automatic reentrant subroutine calling.

#### Instruction Set

The instruction complement uses the flexibility of the general-purpose registers to provide over 400 powerful hard-wired instructions -- the most comprehensive and powerful instruction repertoire of any computer in the 16-bit class. Unlike conventional 16-bit computers, which usually have three classes of instructions (memory reference instructions, operate or AC control instructions and I/O instructions) all operations in the PDP-11 are accomplished with one set of instructions. Since peripheral device registers can be manipulated as flexibly as core memory by the central processor, instructions that are used to manipulate data in core memory may be used equally well for data in peripheral device registers. For example, data in an external device register can be tested or modified directly by the CPU, without bringing it into memory or disturbing the general registers. One can add data directly to a peripheral device register, or compare logically or arithmetically contents with a mask and branch. Thus all PDP-11 instructions can be used to create a new dimension in the treatment of computer I/O and the need for a special class of I/O instructions is eliminated. PDP 11/20 instructions are described in Chapter 4.

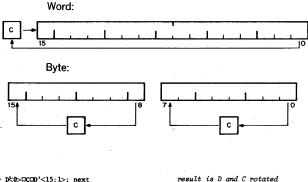

The following example contrasts the rotate operation in the PDP-11 with a similar operation in a conventional minicomputer:

#### PDP-11 Approach

ROR A

; rotate contents of memory location A right one place

#### **Conventional Approach**

LDA A

;load contents of memory location A into AC

#### ;rotate contents of AC right one place

#### ROR

STA A

store contents of AC in location A

The basic order code of the PDP-11 uses both single and double operand address instructions for words or bytes. The PDP-11 therefore performs very efficiently in one step, such operations as adding or subtracting two operands, or moving an operand from one location to another:

#### PDP-11 Approach

#### ADD A,B

; add contents of location A to location B

Alexal Assesses to

|       | Conventional Approach                     |

|-------|-------------------------------------------|

| LDA A | ;load contents of memory location into AC |

| ADD B | ;add cntents of memory location B to AC   |

| STA B | ;store results at location B              |

#### Priority Interrupts

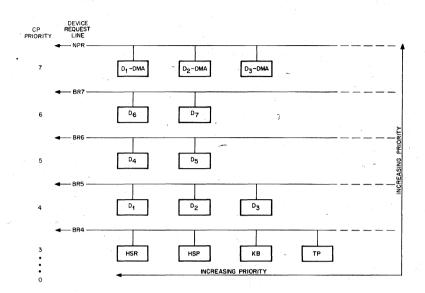

A multi-line automatic priority interrupt system permits the processor to respond automatically to conditions outside the system, Any number of separate devices can be attached to each line. The PDP-11/15 has only a single line of interrupt (any number of devices). A multi-line system, like that of the PDP-11/20, is optional on the PDP-11/15 (KF11-A).

Each peripheral device in the PDP-11 system has a hardware pointer to its own pair of memory words (one points to the devices's service routine, and the other contains the new status processor information). This unique identification eliminates the need for polling of devices to identify an interrupt, since the interrupt servicing hardware selects and begins executing the appropriate service routine after having automatically saved the status of the interrupted program segment.

The devices' interrupt priority and service routine priority are independent. This allows adjustment of system behavior in response to real-time conditions, by dynamically changing the priority level of the service routine.

The interrupt system allows the processor to continually compare its own programmable priority with the priority of any interrupting devices and to acknowledge the device with the highest level above the processors priority level. Servicing an interrupt for a device can be interrupted for servicing a higher priority device. Service to the lower priority device is resumed automatically upon completion of the higher level servicing. Such a process, called nested interrupt servicing, can be carried out to any level without requiring the software to save and restore processor status at each level.

The interrupt scheme is explained in paragraph 2.7, Chapter 2.

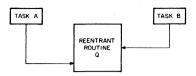

#### Reentrant Code

Both the interrupt handling hardware and the subroutine call hardware facilitate writing reentrant code for the PDP-11. This type of code allows a single copy of a given subroutine or program to be shared by more than one process or task. This

4

reduces the amount of core needed for multi-task applications such as the concurrent servicing of many peripheral devices.

#### Addressing

Much of the power of the PDP-11 is derived from its wide range of addressing capabilities. PDP-11 addressing modes include list sequential addressing, full address indexing, full 16-bit word addressing, 8-bit byte addressing, and stack addressing. Variable length instruction formatting allows a minimum number of bits to be used for each addressing mode. This results in efficient use of program storage space. Addressing modes are described in Chapter 3.

#### Stacks

In the PDP-11, a stack is a temporary data storage area which allows a program to make efficient use of frequently accessed data. The stack is used automatically by program interrupts, subroutine calls, and trap instructions. When the processor is interrupted, the central processor status word and the program counter are saved (pushed) onto the stack area, while the processor services the interrupting device. A new status word is then automatically acquired from an area in core memory which is reserved for interrupt instructions (vector area). A return from the interrupt instruction restores the original processor status and returns to the interrupted program without software intervention. Stacks are explained in Chapter 5.

#### **Direct Memory Access**

All PDP-11's provide for direct access to memory. Any number of DMA devices may be attached to the UNIBUS. Maximum priority is given to DMA devices thus allowing memory data storage or retrieval at memory cycle speeds. Latency is minimized by the organization and logic of the UNIBUS, which samples requests and priorities in parallel with data transfers.

#### **Power Fail and Restart**

The PDP-11's power fail and restart system not only protects memory when power fails, but also allows the user to save the existing program location and status (including all dynamic registers), thus preventing harm to devices, and eliminating the need for reloading programs. Automatic restart is accomplished when power returns to safe operating levels, enabling remote or unattended operations of PDP-11 systems. All standard peripherals in the PDP-11 family are included in the systemized power-fail protect/restart feature. This feature is optional on the PDP-11/15 (KP11-A). Power Fail is discussed in Chapter 2, paragraph 2.

#### 1.2.3 Memories

Memories with different ranges of speeds and various characteristics can be freely mixed and interchanged in a single PDP-11 system. Thus as memory needs expand and as memory technology grows, a PDP-11 can evolve with none of the growing pains and obsolescence associated with conventional computers. See Chapter 2, paragraph 2.5

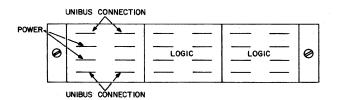

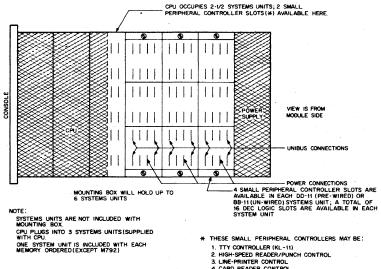

#### 1.2.4 Packaging

The PDP-11 has adopted a modular approach to allow custom configuring of systems, easy expansion, and easy servicing. Systems are composed of basic building blocks, called System Units, which are completely independent subsystems connected only by pluggable UNIBUS and power connections. There is no fixed wiring between them. An example of this type of subsystem is a 4,096-word memory module. System Units can be mounted in many combinations within the PDP-11 hardware, since there are no fixed positions for memory or I/O device controllers. Additional units can be mounted easily and connected to the system in the field. In case maintenance is required, defective System Units can be replaced with spares and operation resumed within a few minutes.

#### **1.3 PERIPHERALS/OPTIONS**

Digital Equipment Corporation (DEC) designs and manufactures many of the peripheral devices offered with PDP-11's. As a designer and manufacturer of peripherals, DEC can offer extremely reliable equipment specifically designed for the small computer environment, lower prices, more choices and quantity discounts.

Many processor, input/output, memory, bus, storage, and communications options are available. These devices are explained in detail in the Peripherals and interfacing Handbook. Options used only by the PDP-11/15, PDP-11/20, and PDP-11R20 are discussed in Chapter 8.

#### 1.3.1 I/O Devices

All PDP-11 systems are available with Teletypes as standard equipment. However, their I/O capabilities can be increased with high speed paper tape readerpunches, line printers, card readers or alphanumeric display terminals. The LA30 DECwriter, a totally DEC-designed and built teleprinter, can serve as an alternative to the Teletype. It has several advantages over standard electromechanical typewriter terminals, including higher speed, fewer mechanical parts and very quiet operation.

PDP-11 I/O devices include:

DECterminal alphanumeric display

**DECwriter teleprinter**

High Speed Line Printers

High Speed Paper Tape Reader and Punch

Teletypes

Card Readers

Synchronous and Asynchronous Communications Interfaces

#### 1.3.2 Storage Devices

Storage devices range from convenient, small-reel magnetic tape (DECtape) units to mass storage magnetic tapes and disk memories. With the UNIBUS, a large number of storage devices, in any combination, may be connected to a PDP-11 system. TU56 DECtapes, highly reliable tape units with small tape reels, designed and built by DEC, are ideal for applications with modest storage requirements. Each DECtape provides storage for 147K 16-bit words. For applications which require handling of large volumes of data, DEC offers the industry compatible TU10 Magtape.

Disk storage devices include fixed head disk units and moving head removable cartridge and disk pack units. These devices range from the 65K RS64 DECdisk memory, to the RP02 Disk Pack system which can store up to 93.6 million words.

PDP-11 storage devices include:

DECtape

Magtape

RS64 65K-256K word fixed-head disk

RS11 256K-2M word fixed-head disk

RK03 1-2M word moving-head disk

RP02 10M word moving head disk

#### 1.3.3 Bus Options

Several options (bus switches, bus extenders) are available for extending the UNI-BUS or for configuring multi-processor or shared-peripheral systems.

#### **1.4 SOFTWARE**

Extensive software, consisting of disk and paper tape systems, is available for PDP-11 Family systems. The larger the PDP-11 configuration, the larger and more comprehensive the software package that comes with it.

#### 1.4.1 Paper Tape Software

The Paper Tape Software system includes:

Editor (ED11)

Assembler (PAL11)

Loaders

On-Line Debugging Technique (ODT11)

Input-Output Executive (IOX)

Math Package (FPP11)

### 1.4.2 Disk Operating System Software

The Disk Operating System software includes:

Text Editor (ED11)

Relocatable Assembler (PAL11R)

Linker (LINK11)

File Utilities Packages (PIP)

On Line Debugging Technique (ODT11)

Librarian (LIBR11)

#### 1.4.3 Higher Level Languages

PDP-11 users needing an interactive conversational language can use BASIC which can be run on the paper tape software system with only 4.096 words of core memory. A multi-user extension of BASIC is available so up to eight users can access a PDP-11 with only 8K of core.

#### RSTS-11

The PDP-11 Resource Timesharing System (RSTS-11) with BASIC-PLUS, an enriched version of BASIC, is available for up to 16 terminal users.

#### FORTRAN

PDP-11 FORTRAN is an ANSI-standard FORTRAN IV compiler with elements that provide easy compatability with IBM 1130 FORTRAN.

#### **1.5 DATA COMMUNICATIONS**

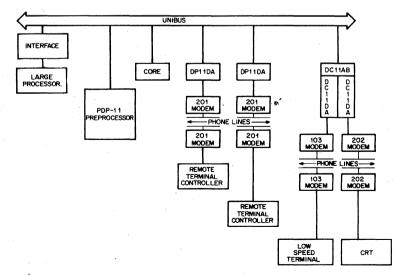

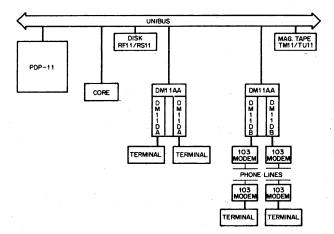

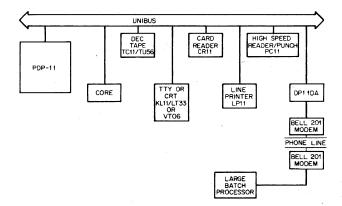

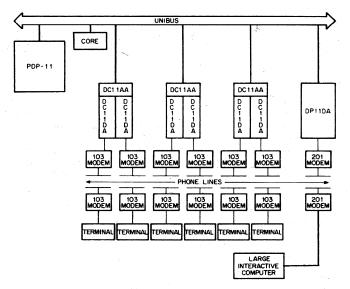

The advanced architecture of PDP-11 Family machines makes them ideal for use in data communications applications. For example, the UNIBUS performs like a multiplexer, and multiple single-line interfaces can be added without special multiplexing hardware; byte handling, the key to communications applications, is accomplished easily and efficiently by the PDP-11. To provide total systems capability in the communications area DEC has developed a full line of communications hardware.

COMTEX-11 software, is described in Part II, Chapter 4; communications hardware is explained in the Peripherals and Interfacing Handbook; and communications applications are discussed in Part III, Chapter 2.

#### **1.6 DATA ACQUISITION CONTROL**

The PDP-11, modular process interfaces and special state-of-the art software (RSX-11C Real-Time Executive) combine to provide efficient, low-cost and reliable systems for industrial data acquisition and control (IDACS) applications. IDACS-11 hardware is described in the Peripherals and Interfacing Handbook. RSX-11C is described in Part II, Chapter 6; and the PDP-11 in data acquisition and control applications is discussed in Part III, Chapter 3.

## PART I CHAPTER 2

## SYSTEM ARCHITECTURE

#### SYSTEM DEFINITION

Digital Equipment Corporation's PDP-11 is a 16-bit, general-purpose, parallel logic computer using two's complement arithmetic. The PDP-11 is a variable word length processor which directly addresses 32,768 16-bit words or 65,536 8-bit bytes. All communication between system components is done on a single high-speed bus called a UNIBUS. Standard features of the system include eight general-purpose registers which can be used as accumulators, index registers, or address pointers, and an automatic priority interrupt system.

#### 2.1 UNIBUS

The UNIBUS is a single, common path that connects the central processor, memory, and all peripherals. Addresses, data, and control information are sent along the 56 lines of the bus.

The form of communication is the same for every device on the UNIBUS. The processor uses the same set of signals to communicate with memory as with peripheral devices. Peripheral devices also use this set of signals when communicating with the processor, memory or other peripheral devices. Each device, including memory locations, processor registers, and peripheral device registers, is assigned an address on the UNIBUS. For example, location 10008 is a core memory location, while location 177562 is the Teletype keyboard data buffer. Thus, peripheral device registers may be manipulated as flexibly as core memory by the central processor. All the instructions that can be applied to data in core memory can be applied equally well to data in peripheral device registers. This is an especially powerful feature, considering the special capability of PDP-11 instructions to process data in any memory location as though it were an accumulator.

#### 2.1.1 Bidirectional Lines

Most UNIBUS lines are bidirectional, so that the same signals that are received as input can be driven as output. This means that a peripheral device register can be either read or loaded by the central processor or other peripheral devices; thus, the same register can be used for both input and output functions.

#### 2.1.2 Master-Slave Relation

Communication between two devices on the bus is in the form of a master-slave relationship. At any point is time, there is one device that has control of the bus. This controlling device is termed the "bus master". The master device controls the bus when communicating with another device on the bus, termed the "slave". A typical example of this relationship is the processor, as master, fetching an instruction from memory (which is always a slave). Another example is the disk, as master, transferring data to memory, as slave. Master-slave relationships are dynamic. The processor, for example, may pass bus control to a disk. The disk, as master, could then communicate with a slave memory bank.

Since the UNIBUS is used by the processor and all I/O devices, there is a priority structure to determine which device gets control of the bus. Every device on the UNIBUS which is capable of becoming bus master is assigned a priority. When two devices, which are capable of becoming a bus master, request use of the bus simultaneously, the device with the higher priority will receive control. The priority structure is further explained in paragraph 2.5 of this Chapter.

#### 2.1.3 Interlocked Communication

Communication on the UNIBUS is interlocked so that for each control signal issued by the master device, there must be a response from the slave in order to complete the transfer. Therefore, communication is independent of the physical bus length (as far as timing is concerned) and the response time of the master and slave devices. This asynchronous operation precludes the need for synchronizing with, and waiting for, clock pulses. Thus, each device is allowed to operate at its maximum possible speed.

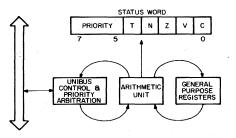

#### 2.2 CENTRAL PROCESSOR

The central processor is organized around three functional blocks: the general purpose registers, arithmetic unit, and UNIBUS and priority control. Data paths connecting these units are in a figure eight. The processor may perform the following data transfers:

register to register memory to memory register to memory memory to register

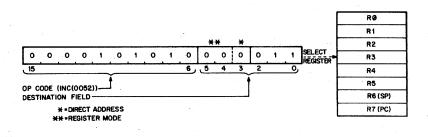

#### 2.2.1 General Registers

The PDP-11/15, PDP-11/20, and PDP-11R20 processors each contain one set of eight general purpose registers. These registers (referred to as R0, R1, R2,...R7) may be used as accumulators, as auto index registers, or as pointers. General Registers R6 and R7 have unique capabilities. R6 serves as the hardware stack pointer, and R7 is the program counter. Using general registers to perform these functions greatly enhances the power and flexibility of the PDP-11. Their use is discussed in Chapter 3 and Chapter 5.

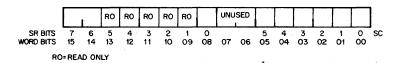

#### 2.2.2 Central Processor Status Register

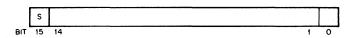

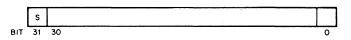

The Central Processor Status Register(PS) contains information on the current priority of the processor, the result of the previous operations, and an indicator

for detecting the execution of an instruction to be trapped during program debugging. The priority of the central processor can be set under program control to any one of five levels. This information is held in bits 5, 6, and 7 of the PS.

Four bits of the PS are assigned to monitoring different results of previous instructions. These bits are set as follows:

Z -- if the result was zero

N -- if the result was negative

C -- if the operation resulted in a carry from the most significant bit

V -- if the operation resulted in an arithmetic overflow

The T bit is used in program debugging and can be set or cleared under program control. If this bit is set, when an instruction is fetched from memory, a processor trap will occur on completion of the instruction's execution.

The processor status word is location 177776 on the UNIBUS and can be operated on by any instruction.

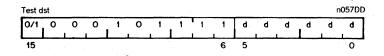

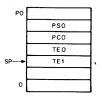

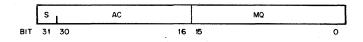

Register organization for PDP-11/20, PDP-11/15 and PDP-11R20:

| GENERAL REGISTERS |    |    |       |        |        |    |      |           |       |    |   |    |          |   |

|-------------------|----|----|-------|--------|--------|----|------|-----------|-------|----|---|----|----------|---|

| RØ                |    |    |       |        |        |    |      |           |       |    |   |    |          |   |

| R1                |    |    |       |        |        |    |      |           |       |    |   |    |          |   |

| R2                |    |    |       |        |        |    |      |           |       |    |   |    |          |   |

| R3                |    |    |       |        |        |    |      |           |       |    |   |    |          |   |

| R4                |    |    | CENTR | AL PRO | OCESSO | RS | τΑΤυ | S REG     | SISTE | R  |   |    |          |   |

| R5                |    | UN | USED  |        |        |    | PR   | IORI      | ΓY    | ΤŢ | N | 7  |          | c |

| R6 (SP)           | L  |    |       |        |        |    | L    | · · · · · | L     |    | L | 1. | <u> </u> | Ľ |

| R7 (PC)           | 15 |    |       |        |        | 8  | 7    | 6         | 5     | 4  | 3 | 2  | -1       | 0 |

#### 2.2.3 Processor States

This description of the KA11 (and KC11) processor is intended only to give the reader a basic description of the processor's operation. More detailed discussion, including theory of operation and logic design, is provided in the KA11 Processor Manual, DEC-11-HR2A-D.

The PDP-11 processor has five major states: fetch, source, destination, execute and service. The first four states are used during normal processor operation; service is used during special operations, such as traps and interrupts.

Fetch: locates and decodes an instruction. When fetch is completed, the processor enters another major state, depending on the type of instruction decoded. It is possible to go from fetch to any other state, including back to fetch. Every instruction starts by first entering the fetch state.

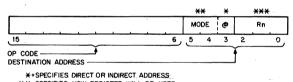

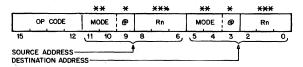

Source: decodes the source field of a double-operand instruction and transfers the source operand to the appropriate location. The source major state is entered only if the instruction is a double-operand type.

Destination: decodes the destination field of the appropriate instruction. Destination fields are present in both single and double-operand instructions. Destination operand is accessed and transferred to appropriate location.

Execute: uses the data obtained during previous major states to perform the specified operation. During this state arithmetic operations, logic functions, and tests are performed, and the Destination location is updated if required.

Service: used to execute special operations, such as interrupts, traps, etc.

Although major states follow the sequence of fetch, source, destination, execute, and service, not all major states are required for every instruction. The processor enters only the states necessary to execute the current instruction. The minimum sequence is from fetch of one instruction directly to fetch of the next instruction. Maximum sequence is fetch, source, destination, execute, service, and back to fetch.

#### 2.2.4 Processor Traps

There are a series of errors and programming conditions which will cause the Central Processor to trap to a set of fixed locations. These include Power Failure, Odd Addressing Errors, Stack Errors, Timeout Errors, Memory Parity Errors, Use of Reserved Instructions, Use of the T bit in the Processor Status Word, and use of the IOT, EMT, and TRAP instructions.

The T bit Trap has already been discussed in this chapter. The IOT, EMT, and TRAP instructions are described in Chapter 4.

#### Power Failure

Whenever AC power drops below 95 volts for 117v nominal power (190 volts for 235 v nominal) or outside a limit of 47 to 63Hz, as measured by DC power, the power fail sequence is initiated. The Central Processor automatically traps to location 24 and the power fail program has 2 msec. to save all volatile information (data in registers), condition peripherals for power fail, and change the contents of location 24 to a pointer to the power-up routine.

When power is restored the processor traps to location 24 and executes the power up routine to restore the machine to its state prior to power failure. Power fail and auto-restart is an option on the PDP-11/15.

#### Odd Addressing Errors

This error occurs whenever a program attempts to execute a word instruction on an odd address (in the middle of a word boundary). The instruction is aborted and the CPU traps through location 4.

#### Time-Out Errors

These errors occur when a Master Synchronization pulse is placed on the UNIBUS and there is no slave pulse within 10  $\mu$ sec. This error usually occurs in attempts to address non-existant memory or peripherals.

The offending instruction is aborted and the processor traps through location 4.

#### **Reserved Instructions**

There is a set of illegal and reserved instructions which cause the processor to trap through location 4.

#### 2.2.5 Trap Handling

Appendix B includes a list of the reserved Trap Vector Locations. When a trap occurs, the processor follows the same procedure for traps as it does for interrupts (saving the Program Counter (PC) and Processor Status Word (PS) on the new Processor Stack etc...)

#### 2.3 CORE MEMORY

#### 2.3.1 Memory Organization

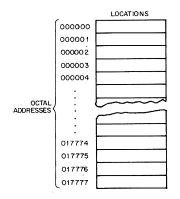

A memory can be viewed as a series of locations, with a number (address) assigned to each location. Thus a 4096-word PDP-11 memory could be shown as follows:

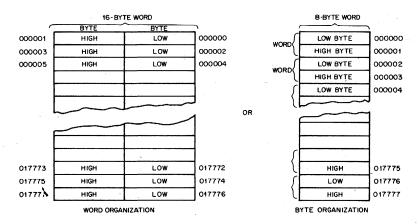

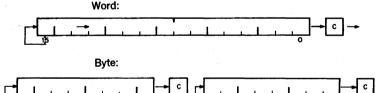

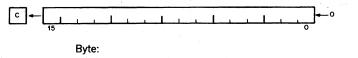

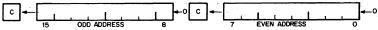

Because PDP-11 memories are designed to accommodate both 16-bit words and 8-bit bytes, the total number of addresses does not correspond to the number of words. A 4096-word memory can contain 8,192 bytes and consists of 017777 octal locations. Words always start at even-numbered locations.

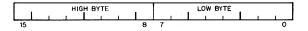

A PDP-11 word is divided into a high byte and a low byte as follows:

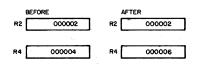

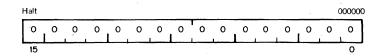

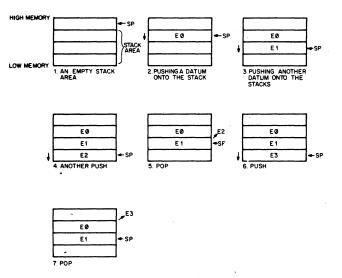

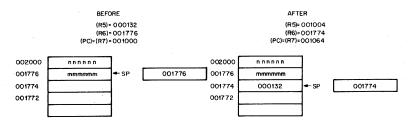

Low bytes are stored at even-numbered memory locations and high bytes at oddnumbered memory locations. Thus it is convenient for the programmer to view the PDP-11 memory as follows: